## 日本国特許庁 JAPAN PATENT OFFICE

別紙添付の書類に記載されている事項は下記の出願書類に記載されている事項と同一であることを証明する。

This is to certify that the annexed is a true copy of the following application as filed with this Office

出願年月日 Date of Application: 2001年

2001年 3月 2日

出 願 番 号 Application Number:

特願2001-058138

出 願 人 Applicant(s):

鹿児島日本電気株式会社

## 2001年 9月 6日

特許庁長官 Commissioner, Japan Patent Office

دھ

出証番号 出証特2001-3082580

## 特2001-058138

| 【書類名】     | 特許願             |  |

|-----------|-----------------|--|

| 【整理番号】    | 00320267        |  |

| 【あて先】     | 特許庁長官殿          |  |

| 【国際特許分類】  | G02F 1/136      |  |

|           | H01L 29/786     |  |

| •         | H01L 21/336     |  |

| 【発明者】     |                 |  |

| 【住所又は居所】  | 鹿児島県出水市大野原町2080 |  |

|           | 鹿児島日本電気株式会社内    |  |

| 【氏名】      | 城戸 秀作           |  |

| 【特許出願人】   |                 |  |

| 【識別番号】    | 000181284       |  |

| 【氏名又は名称】  | 鹿児島日本電気株式会社     |  |

| 【代理人】     |                 |  |

| 【識別番号】    | 100082935       |  |

| 【弁理士】     |                 |  |

| 【氏名又は名称】  | 京本 直樹           |  |

| 【電話番号】    | 03-3454-1111    |  |

| 【選任した代理人】 |                 |  |

| 【識別番号】    | 100082924       |  |

| 【弁理士】     |                 |  |

| 【氏名又は名称】  | 福田 修一           |  |

| 【電話番号】    | 03-3454-1111    |  |

| 【選任した代理人】 |                 |  |

| 【識別番号】    | 100085268       |  |

| 【弁理士】     |                 |  |

| 【氏名又は名称】  | 河合 信明           |  |

| 【電話番号】    | 03-3454-1111    |  |

· 1

【手数料の表示】

| 【予納台帳番号】  | 021566  |

|-----------|---------|

| 【納付金額】    | 21,000円 |

| 【提出物件の目録】 |         |

| 【物件名】     | 明細書 1   |

| 【物件名】     | 図面 1    |

| 【物件名】     | 要約書 1   |

| 【包括委任状番号】 | 9114163 |

| 【プルーフの要否】 | 要       |

e

يەن

出証特2001-3082580

【書類名】 明細書

► / í

【発明の名称】 パターン形成方法及びそれを用いた液晶表示装置の製造方法 【特許請求の範囲】

【請求項1】 被エッチング膜上に第1レジスト膜及び第2レジスト膜を順 に堆積し、前記第1レジスト膜のみの領域と前記第1レジスト膜の上に前記第2 レジスト膜が積層した領域が前記第1レジスト膜で連結した形状に前記第1レジ スト膜及び前記第2レジスト膜をパターニングして第1のレジストマスクを形成 する工程と、前記第1のレジストマスクをマスクとして前記被エッチング膜に1 回目のエッチングを行う工程と、前記第1のレジストマスクをエッチングして前 記第1レジスト膜のみからなる領域を除去し、前記第1のレジストマスクを前記 第1レジスト膜及び前記第2レジスト膜からなる残存レジストマスクとして残す 工程と、前記残存レジストマスクをマスクとして前記被エッチング膜に2回目の エッチングを行う工程と、を有するパターン形成方法であって、前記残存レジス トマスクを形成する工程が、前記第1のレジストマスクのうち前記第1レジスト 膜のみからなる領域を除去するときには前記第2レジスト膜の少なくとも一部が 前記第1レジスト膜よりもエッチング耐性のあるレジスト膜となっていることを 特徴とするパターン形成方法。

【請求項2】 被エッチング膜上に第1レジスト膜及び第2レジスト膜を順 に堆積し、前記第1レジスト膜及び前記第2レジスト膜にそれぞれ第1開口部及 び第2開口部を形成して、第2開口部が第1開口部を包含する形に第1のレジス トマスクを形成する工程と、前記第1のレジストマスクをマスクとして前記被エ ッチング膜をエッチングする工程と、前記第1レジスト膜のうち少なくとも前記 第2開口部に露出した領域を除去して前記第1のレジストマスクを残存レジスト マスクとして残す工程と、前記被エッチング膜、前記残存レジストマスクの上に 所定の材料膜を堆積させる工程と、前記残存レジストマスクを除去して前記残存 レジストマスクの上の材料膜を除去する工程とを有するパターン形成方法であっ て、前記第1のレジストマスクを残存レジストマスクとして残す工程が、前記第 1レジスト膜を除去するときには前記第2レジスト膜の少なくとも一部が前記第 1レジスト膜よりもエッチング耐性のあるレジスト膜となっていることを特徴と

するパターン形成方法。

【請求項3】 前記第1のレジストマスクを形成する工程において、前記被 エッチング膜上に第1レジスト膜及び第2レジスト膜を順に堆積する際、前記第 2レジスト膜の少なくとも一部が、前記第1レジスト膜よりもエッチング耐性の あるレジスト膜として形成される請求項1又は2記載のパターン形成方法

【請求項4】 前記残存レジストマスクを形成する工程において、前記第2 レジスト膜の少なくとも一部が、前記第1レジスト膜よりもエッチング耐性のあ る改質レジスト膜とされた後に、前記第2レジスト膜に覆われない前記第1レジ スト膜をエッチング除去することにより行われる請求項1又は2記載のパターン 形成方法。

【請求項5】 前記エッチング耐性が、ドライエッチングに対するエッチン グ耐性である請求項1乃至4のいずれかに記載のパターン形成方法。

【請求項6】 前記ドライエッチングが、O<sub>2</sub>ガスを含むプラズマ処理ガス、フッ素系ガスを含むプラズマ処理ガス、O<sub>2</sub>ガスとフッ素系ガスを含むプラズマ処理ガス、マ処理ガスのいずれかのプラズマ処理ガスを用いて行われる含む請求項5記載のパターン形成方法。

【請求項7】 前記プラズマ処理ガスがフッ素系ガスであるときは、SF<sub>6</sub>、CF<sub>4</sub>、CHF<sub>3</sub>のいずれかを含むガスであり、前記プラズマ処理ガスがO<sub>2</sub>ガスとフッ素系ガスの混合ガスであるときは、SF<sub>6</sub> $/O_2$ 、CF<sub>4</sub> $/O_2$ 、CHF<sub>3</sub> $/O_2$ のいずれかのガスを含む請求項6記載のパターン形成方法。

【請求項8】 前記エッチング耐性が、ウェットエッチングに対するエッチ ング耐性である請求項1乃至4のいずれかに記載のパターン形成方法。

【請求項9】 前記ウェットエッチングが、アルカリ溶液を用いたエッチン グ処理である請求項8記載のパターン形成方法。

【請求項10】 前記アルカリ溶液が、テトラメチルアンモニウムハイドロ オキサイド、コリン、有機アミンのいずれかを含む有機アルカリ溶液である請求 項9記載のパターン形成方法。

【請求項11】 前記アルカリ溶液が、KOH、NAOH、Ca(OH) 2、CaCO<sub>3</sub>のいずれかを含む無機アルカリ溶液である請求項9記載のパターン

形成方法。

【請求項12】 前記第1レジスト膜として有機レジスト膜、前記第2レジ スト膜として無機レジスト膜を用いる請求項1乃至11のいずれかに記載のパタ ーン形成方法。

【請求項13】 前記第2レジスト膜の少なくとも一部は、シリコン含有の レジスト膜からなる請求項1乃至11のいずれかに記載のパターン形成方法。

【請求項14】 前記改質レジスト膜を形成する工程が、前記第2レジスト 膜の中にシリコンを含有させて前記第2レジスト膜の少なくとも一部をシリコン 含有第2レジスト膜とし、少なくとも酸素を含む混合ガス中でのドライエッチン グ処理により前記シリコン含有第2レジスト膜をシリコン酸化膜に変換すること により行われる請求項5乃至13記載のパターン形成方法。

【請求項15】 前記改質レジスト膜を形成する工程が、前記第2レジスト 膜の中にシリコンを含有させて前記第2レジスト膜の少なくとも一部をシリコン 含有第2レジスト膜とし、少なくとも酸素を含む混合ガス中でのドライエッチン グ処理により前記シリコン含有第2レジスト膜をシリコン酸化膜に変換すると共 に、前記第2レジスト膜が形成された領域以外の領域の第1レジスト膜を除去す ることにより行われる請求項5乃至13記載のパターン形成方法。

【請求項16】 前記第2レジスト膜の少なくとも一部が、シリル化が可能 なレジスト膜からなる請求項14又は15記載のパターン形成方法。

【請求項17】 前記第2シリコン含有レジスト膜を形成する工程が、前記 第1レジスト膜及び前記第2レジスト膜をシラザンを含むシリル化剤に浸漬し、 前記第2レジスト膜のみをシリル化させることにより行われる請求項14、15 又は16記載のパターン形成方法。

【請求項18】 前記少なくとも酸素を含む混合ガスは、O<sub>2</sub>ガスと不活性 ガスとの混合ガス、O<sub>2</sub>ガスとフッ素系ガスとの混合ガスのいずれかの混合ガス である請求項14乃至17のいずれかに記載のパターン形成方法。

【請求項19】 前記酸素を含む混合ガスが $O_2$ ガスと不活性ガスであると きは、 $O_2$ /He、 $O_2$ /Arのいずれかの混合ガスであり、 $O_2$ ガスとフッ素系 ガスであるときは、 $O_2$ /SF<sub>6</sub>、 $O_2$ /CF<sub>4</sub>、 $O_2$ /CHF<sub>3</sub>のいずれかの混合ガ

スである請求項18記載のパターン形成方法。

【請求項20】 第1レジスト膜上に形成された第2レジスト膜から部分的 に前記第1レジスト膜が露出する構成の第1のレジストマスクを被エッチング膜 上に形成する工程と、前記第1のレジストマスクをマスクとして前記被エッチン グ膜に1回目のエッチングを行う工程と、前記露出する第1レジスト膜領域をエ ッチング除去することにより前記第1レジスト膜と前記第2レジスト膜との積層 部からなる残存レジストマスクを形成する工程と、前記残存レジストマスクをマ スクとして前記被エッチング膜に2回目のエッチングを行う工程と、を有するパ ターン形成方法であって、前記露出する第1レジスト膜領域を除去する工程にお いて、前記第2レジスト膜の少なくとも一部が前記第1レジスト膜よりもエッチ ング耐性のあるレジスト膜となっていることを特徴とするパターン形成方法。

【請求項21】 第1基板上にゲート配線及びゲート電極を形成し、続いて 、前記第1基板上に前記ゲート配線及び前記ゲート電極を覆うゲート絶縁膜を形 成する工程と、前記ゲート絶縁膜上に下から順に半導体膜、不純物ドープ半導体 膜、ソース・ドレイン用金属膜を堆積させる工程と、前記ソース・ドレイン用金 属膜上に第1レジスト膜及び第2レジスト膜を順に堆積し、前記第1レジスト膜 のみの領域と前記第1レジスト膜の上に前記第2レジスト膜が積層した領域が前 記第1レジスト膜で連結した形状に前記第1レジスト膜及び前記第2レジスト膜 をパターニングし前記第1レジスト膜のみからなる領域をTFTのチャネル形成 予定領域の上方に位置するよう第1のレジストマスクを形成する工程と、前記第 1のレジストマスクをマスクとして、少なくとも前記ソース・ドレイン用金属膜 をエッチング除去して前記ソース・ドレイン用金属膜からなる電極パターンを形 成する工程と、前記第1のレジストマスクをエッチングして前記第1レジスト膜 のみからなる領域を除去し、前記第1のレジストマスクを前記第1レジスト膜及 び前記第2レジスト膜からなる残存レジストマスクとして残して前記第1レジス ト膜のみからなる領域の下の前記ソース・ドレイン用金属膜を露出させる工程と 、前記残存レジストマスクをマスクとして、前記第1レジスト膜のみからなる領 域の下の前記ソース・ドレイン用金属膜、前記不純物ドープ半導体膜及び前記半 導体膜を選択的にエッチングして前記ソース・ドレイン用金属膜及びその下の不

出証特2001-3082580

特2001-058138

純物ドープ半導体膜を少なくとも除去してTFTのチャネル領域を形成すると同 時にドレイン電極を含むドレイン配線及びソース電極を形成する工程とを有する 製造方法によりTFT基板を形成し、続いて、前記第1基板の前記TFTの形成 された側に前記第1基板と対向する第2基板を配置して対向基板を形成し、さら に、前記TFT基板と前記対向基板との間に液晶組成物を充填する液晶表示装置 の製造方法において、前記残存レジストマスクを形成する工程が、前記第1のレ ジストマスクのうち前記第1レジスト膜のみからなる領域を除去するときには前 記第2レジスト膜の少なくとも一部が前記第1レジスト膜よりもエッチング耐性 のあるレジスト膜となっていることを特徴とする液晶表示装置の製造方法。

【請求項22】 前記ゲート配線及びゲート電極を形成する工程において、 前記ゲート配線及びゲート電極と共に櫛歯状の共通電極を形成し、前記第1のレ ジストマスクを形成する工程において、前記共通電極の櫛歯状の電極間に画素電 極が形成されるべく画素電極形成用に画素電極形成予定領域のソース・ドレイン 用金属膜上にも前記第1のレジストマスクが形成される請求項21記載の液晶表 示装置の製造方法。

【請求項23】 前記第1のレジストマスクを形成する工程において、前記 ソース・ドレイン用金属膜上に第1レジスト膜及び第2レジスト膜を順に堆積す る際、前記第2レジスト膜の少なくとも一部が、前記第1レジスト膜よりもエッ チング耐性のあるレジスト膜として堆積される請求項21又は22記載の液晶表 示装置の製造方法。

【請求項24】 前記残存レジストマスクを形成する工程において、前記第 1のレジストマスクのうち前記第2レジスト膜の少なくとも一部が、前記第1レ ジスト膜よりもエッチング耐性のある改質レジスト膜とされた後に、前記第1レ ジスト膜のみからなる領域をエッチング除去することにより行われる請求項21 又は22記載の液晶表示装置の製造方法。

【請求項25】 前記改質レジスト膜の形成が、前記第2レジスト膜の中に シリコンを含有させて前記第2レジスト膜の少なくとも一部をシリコン含有第2 レジスト膜とし、少なくとも酸素を含む混合ガス中でのドライエッチング処理に より前記シリコン含有第2レジスト膜をシリコン酸化膜に変換すると共に、前記

第1レジスト膜のみからなる領域を除去することにより行われる請求項24記載 の液晶表示装置の製造方法。

【請求項26】 前記チャネル領域を形成する工程の後に、前記TFTのチ ャネル領域を形成する際に用いられた前記残存レジストマスクを除去し、続いて 、前記ゲート絶縁膜を覆う保護絶縁膜を堆積させる工程と、前記保護絶縁膜上に 第3レジスト膜及び第4レジスト膜を順に堆積し、前記ドレイン配線を取り出す ドレイン端子の上方の開口予定領域の第4レジスト膜を除去して前記ドレイン端 子の上方の開口予定領域に第3レジスト膜のみを残し、前記ゲート端子の上方の 開口予定領域の第3 レジスト膜及び第4 レジスト膜を除去して前記ゲート端子の 上方の開口予定領域の保護絶縁膜を露出させる工程と、前記第4 レジスト膜をマ スクとして前記ゲート端子上の保護絶縁膜及びゲート絶縁膜からなる絶縁膜の一 部をエッチングしながら前記ドレイン端子上の第3レジスト膜を除去すると共に 、前記第4レジスト膜及びその下の前記第3レジスト膜を残す工程と、前記第4 レジスト膜及びその下の前記第3レジスト膜をマスクとして前記ドレイン端子の 上の保護絶縁膜を除去すると共に前記ゲート端子上に残る絶縁膜を除去する工程 とを有し、前記第4レジスト膜及びその下の前記第3レジスト膜を残す工程が、 前記第4 レジスト膜の中にシリコンを含有させて前記第4 レジスト膜をシリコン 含有第4レジスト膜とし、前記ドレイン端子上の前記第3レジスト膜の除去が、 酸素ガス中でのドライエッチング処理により前記シリコン含有第4 レジスト膜を シリコン酸化膜に変換すると共に、前記ドレイン端子の上方の開口予定領域に位 置する第3レジスト膜を除去することにより行われる請求項21乃至25のいず れかに記載の液晶表示装置の製造方法。

【請求項27】 前記チャネル領域を形成する工程の後に、前記TFTのチャネル領域を形成する際に用いられた前記残存レジストマスクを除去し、続いて、前記ゲート絶縁膜を覆う保護絶縁膜を堆積させる工程と、前記保護絶縁膜上に 第3レジスト膜及び第4レジスト膜を順に堆積し、前記第3レジスト膜及び前記 第4レジスト膜を開口して前記ゲート端子及び前記ドレイン端子上方に第4レジ スト膜の開口部が第3レジスト膜の開口部を包含する形に形成する工程と、前記 第3レジスト膜及び前記第4レジスト膜をマスクとして前記ゲート端子上の保護

絶縁膜及びゲート絶縁膜、前記ドレイン端子上の保護絶縁膜をそれぞれ除去して コンタクトホールを形成する工程と、前記第4レジスト膜の開口部に露出してい る第3レジスト膜をエッチング除去すると共に、前記第4レジスト膜及びその下 の第3レジスト膜を残す工程と、前記第4レジスト膜及びその下の第3レジスト 膜を及び前記コンタクトホールを覆って上層金属膜を堆積させる工程と、前記第 4レジスト膜及びその下の第3レジスト膜を除去して前記第4レジスト膜及びそ の下の第3レジスト膜の上の前記上層金属膜を除去し前記コンタクトホールを覆 う上部電極を形成する工程とを有し、前記第4レジスト膜及びその下の第3レジ スト膜を形成する工程が、前記第4レジスト膜の中にシリコンを含有させて前記 第4レジスト膜をシリコン含有第4レジスト膜とし、前記第4レジスト膜の開口 部に露出している第3レジスト膜の除去が、酸素を含む混合ガス中でのドライエ ッチング処理により前記シリコン含有第4レジスト膜をシリコン酸化膜に変換す ると共に、前記シリコン酸化膜に覆われない第3レジスト膜を除去することによ り行われる請求項21乃至25のいずれかに記載の液晶表示装置の製造方法。

【請求項28】 前記保護絶縁膜上に第3レジスト膜及び第4レジスト膜を 順に堆積する工程において、前記第4レジスト膜の少なくとも一部が、前記第3 レジスト膜よりもエッチング耐性のあるレジスト膜として堆積される請求項26 又は27記載の液晶表示装置の製造方法。

【請求項29】 前記第4レジスト膜及びその下の前記第3レジスト膜を残 す工程において、前記第4レジスト膜の少なくとも一部が、前記第3レジスト膜 よりもエッチング耐性のある改質レジスト膜とされた後に、前記第4レジスト膜 に覆われない第3レジスト膜をエッチング除去することにより行われる請求項2 6又は27記載の液晶表示装置の製造方法。

【請求項30】 前記改質レジスト膜の形成が、前記第4レジスト膜の中に シリコンを含有させて前記第4レジスト膜の少なくとも一部をシリコン含有第4 レジスト膜とし、少なくとも酸素を含む混合ガス中でのドライエッチング処理に より前記シリコン含有第4レジスト膜をシリコン酸化膜に変換すると共に、前記 第4レジスト膜に覆われない第3レジスト膜を除去することにより行われる請求 項29記載の液晶表示装置の製造方法。

. 7

【発明の詳細な説明】

[0001]

【発明の属する技術分野】

本発明は、半導体素子用のパターン形成方法及びそれを用いた液晶表示装置の 製造方法に関し、従来の2PR工程を1PR工程で済ませる製造工程短縮プロセ スに関する。

[0, 0, 0, 2]

【従来の技術】

半導体装置の高集積化は、微細パターンの形成手段であるフォトリソグラフィ 技術とドライエッチング技術とに支えられて達成されてきた。しかし、このよう にして半導体装置が高性能化されてくると、その製造工程が高度化し製造コスト が増加するようになる。

[0003]

そこで、最近では、半導体装置の製造コストを大幅に低減すべく、パターンの 製造工程を短絡させて全体の工程数を短縮させることが強く要求されてきている 。この要求に対応する技術として、従来2つ以上必要とされたPR工程を1つの PR工程で済ませる方法が種々開示されている。

【0004】

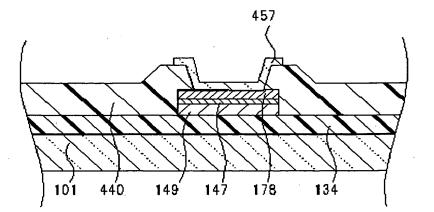

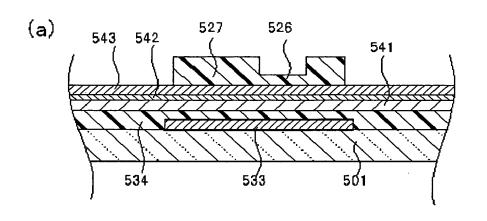

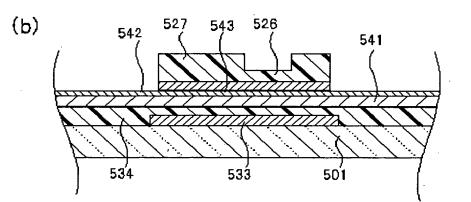

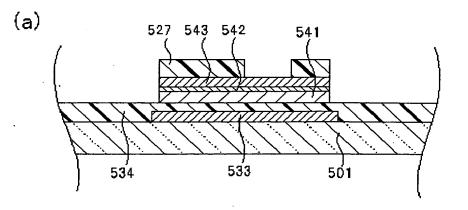

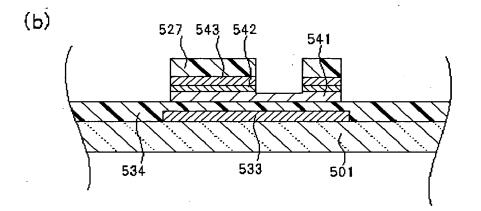

第1の従来例(特開2000-206571号公報)は、この方法を逆スタガ ード型薄膜トランジスタ(以下「TFT」という。)の製造方法に適用したもの であり、図23、24はその主要製造工程を製造工程順に示すTFT近傍の模式 断面図である。

[0005]

出証特2001-3082580

[0006]

次に、図23(b)に示すように、感光膜パターン527と感光膜パターン526をマスクとして、金属膜543をエッチング除去して、n<sup>+</sup>型a-Si膜542を露出させる。

[0007]

次に、図24 (a)に示すように、 n<sup>+</sup>型 a − S i 膜542とその下部の a − S i 膜541を感光膜パターン526と共にドライエッチングし、残った感光膜 パターン527の間に金属膜543を露出させる。

$\begin{bmatrix} 0 & 0 & 0 \\ 0 & 0 & 0 \end{bmatrix}$

次に、図24(b)に示すように、残った感光膜パターン527をマスクとして金属膜543とその下の $n^+$ 型a-Si膜542をエッチング除去する。このときa-Si膜541も一部エッチングされる。

[0009]

以上のようにして、膜厚の異なる感光膜パターン527と感光膜パターン52 6を利用すると、被エッチング膜に2つの異なるパターンを形成することができ る。

[0010]

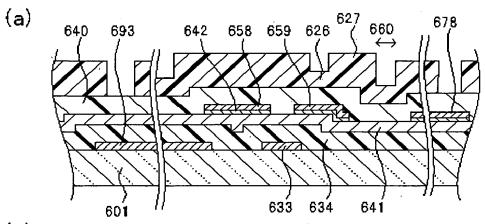

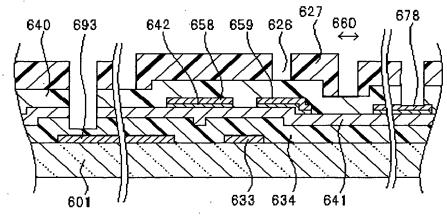

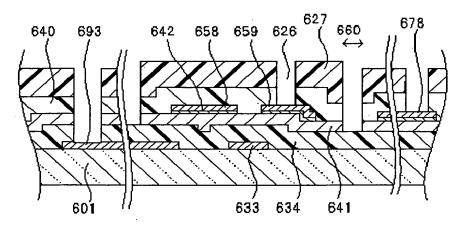

次に示す第2の従来例(特開2000-164584号公報)は、やはりこの 方法を逆スタガード型TFTの製造方法に適用したものであり、図25はその主 要製造工程を製造工程順に示すTFT近傍、ゲート端子電極及びドレイン端子電 極の模式断面図である。

[0011]

まず、図25(a)に示すように、第1透明基板601の上にゲート電極63 3、ゲート端子電極693、ゲート絶縁膜634が形成され、続いて、a-Si 膜641、n<sup>+</sup>型a-Si膜642、ソース・ドレイン用の金属膜を順に堆積し 、さらに金属膜及びその下のn<sup>+</sup>型a-Si膜642を同じパターンにパターニ ングして、ソース電極659及びその下のオーミック層とドレイン電極658及 びその下のオーミック層、ドレイン端子電極678及びその下のオーミック層を 形成する。これらを覆うパッシベーション膜640を形成した後、ゲート端子電

出証特2001-3082580

## 特2001-058138

極693とドレイン端子電極678の上に開口を有し、ソース電極659及びそ の横のa-Si膜分離部660に厚さの薄い感光膜パターン626を、その他の 領域には厚さの厚い感光膜パターン627を有するレジストパターンを形成する

[0012]

次に、図25(b)に示すように、このレジストパターンを利用し、かつ、エ ッチング条件を最適化しながら、まず薄い感光膜パターン626が除去される時 間エッチングを行って、ドレイン端子電極678の上のパッシベーション膜64 0を完全に除去し、ゲート端子電極693の上のパッシベーション膜640の全 部とゲート絶縁膜634の一部を除去する。

[0013]

さらに、エッチング条件を最適化しながら、図25(c)に示すように、 a – S i 膜分離部660のa – S i 膜641が除去され、同時に、ゲート端子電極693の上に残っていたゲート絶縁膜634の一部を除去する。

[0014]

以上のようにして、第2の従来例では、レジスト膜の厚さの違いを利用して、 各電極上のコンタクトホールの形成を1回のPR工程で済ませると共に、 a - S i 膜の分離を行っている。

【0015】

【発明が解決しようとする課題】

以上に説明した第1の従来例及び第2の従来例は、いずれも被エッチング膜上 に1層の感光膜を塗布した後に、露光量の違いを利用して膜厚の異なる感光膜パ ターンを形成し、その膜厚の差を利用して被エッチング膜をエッチングして製造 工程の短縮を図っている。

[0016]

然るに、第1の従来例及び第2の従来例において、感光膜パターンのうち薄い 方の感光膜パターンがエッチング除去されたときに厚い方の感光膜パターンも同 時にエッチングされ、その形状はエッチング前の形状とは大幅に異なってしまい 、エッチング中においてもその形状が時間と共に変化していくという問題がある

出証特2001-3082580

。従って、厚い方の感光膜パターンをマスクとしてエッチングされる被エッチン グ膜の形状は、設計された形状とは大幅に異なる形状となることが推測される。

[0017]

本発明は、感光膜(以下レジストと呼ぶ)パターンの膜厚の違いを利用して被 エッチング膜をエッチングする際に、厚い方のレジストパターンが薄い方のレジ ストパターンをエッチング除去するためのエッチングに晒されても、その形状を 維持できるパターン形成方法及びそれを用いた液晶表示装置の製造方法を提供す ることにある。

[0018]

【課題を解決するための手段】

本発明の第1のパターン形成方法は、被エッチング膜上に第1レジスト膜及び 第2レジスト膜を順に堆積し、前記第1レジスト膜のみの領域と前記第1レジス ト膜の上に前記第2レジスト膜が積層した領域が前記第1レジスト膜で連結した 形状に前記第1レジスト膜及び前記第2レジスト膜をパターニングして第1のレ ジストマスクを形成する工程と、前記第1のレジストマスクをマスクとして前記 被エッチング膜に1回目のエッチングを行う工程と、前記第1のレジストマスク をエッチングして前記第1レジスト膜のみからなる領域を除去し、前記第1のレ ジストマスクを前記第1レジスト膜及び前記第2レジスト膜からなる残存レジス トマスクとして残す工程と、前記残存レジストマスクをマスクとして前記被エッ チング膜に2回目のエッチングを行う工程と、を有するパターン形成方法であっ て、前記残存レジストマスクを形成する工程が、前記第1のレジストマスクのう ち前記第1レジスト膜のみからなる領域を除去するときには前記第2レジスト膜 の少なくとも一部が前記第1レジスト膜よりもエッチング耐性のあるレジスト膜 となっていることを特徴とする。

[0019]

本発明の第2のパターン形成方法は、被エッチング膜上に第1レジスト膜及び 第2レジスト膜を順に堆積し、前記第1レジスト膜及び前記第2レジスト膜にそ れぞれ第1開口部及び第2開口部を形成して、第2開口部が第1開口部を包含す る形に第1のレジストマスクを形成する工程と、前記第1のレジストマスクをマ

出証特2001-3082580

特2001-058138

スクとして前記被エッチング膜をエッチングする工程と、前記第1レジスト膜の うち少なくとも前記第2開口部に露出した領域を除去して前記第1のレジストマ スクを残存レジストマスクとして残す工程と、前記被エッチング膜、前記残存レ ジストマスクの上に所定の材料膜を堆積させる工程と、前記残存レジストマスク を除去して前記残存レジストマスクの上の材料膜を除去する工程とを有するパタ ーン形成方法であって、前記第1のレジストマスクを残存レジストマスクとして 残す工程が、前記第1レジスト膜を除去するときには前記第2レジスト膜の少な くとも一部が前記第1レジスト膜よりもエッチング耐性のあるレジスト膜となっ ていることを特徴とする。

[0020]

上記本発明の第1、2のパターン形成方法は、前記第1のレジストマスクを形成する工程において、前記被エッチング膜上に第1レジスト膜及び第2レジスト 膜を順に堆積する際、前記第2レジスト膜の少なくとも一部が、前記第1レジス ト膜よりもエッチング耐性のあるレジスト膜として形成され、前記残存レジスト マスクを形成する工程において、前記第2レジスト膜の少なくとも一部が、前記 第1レジスト膜よりもエッチング耐性のある改質レジスト膜とされた後に、前記 第2レジスト膜に覆われない前記第1レジスト膜をエッチング除去することによ り行われ、前記エッチング耐性が、ドライエッチングに対するエッチング耐性で あり、前記ドライエッチングが、O<sub>2</sub>ガスを含むプラズマ処理ガス、フッ素系ガ スを含むプラズマ処理ガス、O<sub>2</sub>ガスとフッ素系ガスを含むプラズマ処理ガスの いずれかのプラズマ処理ガスを用いて行われ、前記プラズマ処理ガスがフッ素系 ガスであるときは、SF<sub>6</sub>、CF<sub>4</sub>、CHF<sub>3</sub>のいずれかを含むガスであり、前記 プラズマ処理ガスがO<sub>2</sub>ガスとフッ素系ガスの混合ガスであるときは、SF<sub>6</sub>/O 2、CF<sub>4</sub>/O<sub>2</sub>、CHF<sub>3</sub>/O<sub>2</sub>のいずれかのガスを含む。

[0021]

また、上記本発明の第1、2のパターン形成方法の前記エッチング耐性が、ウ エットエッチングに対するエッチング耐性であるときは、前記ウェットエッチン グが、アルカリ溶液を用いたエッチング処理であり、前記アルカリ溶液が、テト ラメチルアンモニウムハイドロオキサイド、コリン、有機アミンのいずれかを含

出証特2001-3082580

$1 \ 2$

む有機アルカリ溶液である、または、KOH、NAOH、Ca(OH)<sub>2</sub>、Ca CO<sub>3</sub>のいずれかを含む無機アルカリ溶液である。

[0022]

また、上記本発明の第1、2のパターン形成方法は、前記第1レジスト膜とし て有機レジスト膜、前記第2レジスト膜として無機レジスト膜を用いる。

[0023]

また、上記本発明の第1、2のパターン形成方法は、前記第2レジスト膜の少 なくとも一部は、シリコン含有のレジスト膜からなり、前記改質レジスト膜を形 成する工程が、前記第2レジスト膜の中にシリコンを含有させて前記第2レジス ト膜の少なくとも一部をシリコン含有第2レジスト膜とし、少なくとも酸素を含 む混合ガス中でのドライエッチング処理により前記シリコン含有第2レジスト膜 をシリコン酸化膜に変換することにより行われる、或いは、前記第2レジスト膜 の中にシリコンを含有させて前記第2レジスト膜の少なくとも一部をシリコン含 有第2レジスト膜とし、少なくとも酸素を含む混合ガス中でのドライエッチング 処理により前記シリコン含有第2レジスト膜をシリコン酸化膜に変換すると共に 、前記第2レジスト膜が形成された領域以外の領域の第1レジスト膜を除去する ことにより行われる。さらに具体的には、前記第2レジスト膜の少なくとも一部 が、シリル化が可能なレジスト膜からなり、前記第2シリコン含有レジスト膜を 形成する工程が、前記第1レジスト膜及び前記第2レジスト膜をシラザンを含む シリル化剤に浸漬し、前記第2レジスト膜のみをシリル化させることにより行わ れ、前記少なくとも酸素を含む混合ガスは、O<sub>2</sub>ガスと不活性ガスとの混合ガス 、O2ガスとフッ素系ガスとの混合ガスのいずれかの混合ガスであり、前記酸素 を含む混合ガスが $O_2$ ガスと不活性ガスであるときは、 $O_2$ /He、 $O_2$ /Arの いずれかの混合ガスであり、O2ガスとフッ素系ガスであるときは、O2/SF6 、 $O_2/CF_4$ 、 $O_2/CHF_3$ のいずれかの混合ガスである。

[0024]

さらに、上記本発明の第1のパターン形成方法は、第1レジスト膜上に形成さ れた第2レジスト膜から部分的に前記第1レジスト膜が露出する構成の第1のレ ジストマスクを被エッチング膜上に形成する工程と、前記第1のレジストマスク

出証特2001-3082580

特2001-058138

をマスクとして前記被エッチング膜に1回目のエッチングを行う工程と、前記露 出する第1レジスト膜領域をエッチング除去することにより前記第1レジスト膜 と前記第2レジスト膜との積層部からなる残存レジストマスクを形成する工程と 、前記残存レジストマスクをマスクとして前記被エッチング膜に2回目のエッチ ングを行う工程と、を有するパターン形成方法であって、前記露出する第1レジ スト膜領域を除去する工程において、前記第2レジスト膜の少なくとも一部が前 記第1レジスト膜よりもエッチング耐性のあるレジスト膜となっている、という 上位概念構成として表すことができる。

[0025]

次に、本発明の液晶表示装置の製造方法は、第1基板上にゲート配線及びゲー ト電極を形成し、続いて、前記第1基板上に前記ゲート配線及び前記ゲート電極 を覆うゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上に下から順に半導体 膜、不純物ドープ半導体膜、ソース・ドレイン用金属膜を堆積させる工程と、前 記ソース・ドレイン用金属膜上に第1レジスト膜及び第2レジスト膜を順に堆積 し、前記第1レジスト膜のみの領域と前記第1レジスト膜の上に前記第2レジス ト膜が積層した領域が前記第1レジスト膜で連結した形状に前記第1レジスト膜 及び前記第2レジスト膜をパターニングし前記第1レジスト膜のみからなる領域 をTFTのチャネル形成予定領域の上方に位置するよう第1のレジストマスクを 形成する工程と、前記第1のレジストマスクをマスクとして、少なくとも前記ソ ース・ドレイン用金属膜をエッチング除去して前記ソース・ドレイン用金属膜か らなる電極パターンを形成する工程と、前記第1のレジストマスクをエッチング して前記第1レジスト膜のみからなる領域を除去し、前記第1のレジストマスク を前記第1レジスト膜及び前記第2レジスト膜からなる残存レジストマスクとし て残して前記第1レジスト膜のみからなる領域の下の前記ソース・ドレイン用金 属膜を露出させる工程と、前記残存レジストマスクをマスクとして、前記第1レ ジスト膜のみからなる領域の下の前記ソース・ドレイン用金属膜、前記不純物ド ープ半導体膜及び前記半導体膜を選択的にエッチングして前記ソース・ドレイン 用金属膜及びその下の不純物ドープ半導体膜を少なくとも除去してTFTのチャ ネル領域を形成すると同時にドレイン電極を含むドレイン配線及びソース電極を

形成する工程とを有する製造方法によりTFT基板を形成し、続いて、前記第1 基板の前記TFTの形成された側に前記第1基板と対向する第2基板を配置して 対向基板を形成し、さらに、前記TFT基板と前記対向基板との間に液晶組成物 を充填する液晶表示装置の製造方法において、前記残存レジストマスクを形成す る工程が、前記第1のレジストマスクのうち前記第1レジスト膜のみからなる領 | 域を除去するときには前記第2レジスト膜の少なくとも一部が前記第1レジスト 膜よりもエッチング耐性のあるレジスト膜となっていることを特徴とし、前記ゲ ート配線及びゲート電極を形成する工程において、前記ゲート配線及びゲート電 極と共に櫛歯状の共通電極を形成し、前記第1のレジストマスクを形成する工程 において、前記共通電極の櫛歯状の電極間に画素電極が形成されるべく画素電極 形成用に画素電極形成予定領域のソース・ドレイン用金属膜上にも前記第1のレ ジストマスクが形成される。また、前記第1のレジストマスクを形成する工程に おいて、前記ソース・ドレイン用金属膜上に第1レジスト膜及び第2レジスト膜 を順に堆積する際、前記第2レジスト膜の少なくとも一部が、前記第1レジスト 膜よりもエッチング耐性のあるレジスト膜として堆積される、或いは、前記残存 レジストマスクを形成する工程において、前記第1のレジストマスクのうち前記 第2レジスト膜の少なくとも一部が、前記第1レジスト膜よりもエッチング耐性 のある改質レジスト膜とされた後に、前記第1レジスト膜のみからなる領域をエ ッチング除去することにより行われ、前記改質レジスト膜の形成が、前記第2レ ジスト膜の中にシリコンを含有させて前記第2レジスト膜の少なくとも一部をシ リコン含有第2レジスト膜とし、少なくとも酸素を含む混合ガス中でのドライエ ッチング処理により前記シリコン含有第2レジスト膜をシリコン酸化膜に変換す ると共に、前記第1レジスト膜のみからなる領域を除去することにより行われる

[0026]

また、本発明の液晶表示装置の製造方法は、前記チャネル領域を形成する工程 の後に、前記TFTのチャネル領域を形成する際に用いられた前記残存レジスト マスクを除去し、続いて、前記ゲート絶縁膜を覆う保護絶縁膜を堆積させる工程 と、前記保護絶縁膜上に第3レジスト膜及び第4レジスト膜を順に堆積し、前記

出証特2001-3082580

ドレイン配線を取り出すドレイン端子の上方の開口予定領域の第4 レジスト膜を 除去して前記ドレイン端子の上方の開口予定領域に第3レジスト膜のみを残し、 前記ゲート端子の上方の開口予定領域の第3レジスト膜及び第4レジスト膜を除 去して前記ゲート端子の上方の開口予定領域の保護絶縁膜を露出させる工程と、 前記第4レジスト膜をマスクとして前記ゲート端子上の保護絶縁膜及びゲート絶 縁膜からなる絶縁膜の一部をエッチングしながら前記ドレイン端子上の第3レジ スト膜を除去すると共に、前記第4 レジスト膜及びその下の前記第3 レジスト膜 を残す工程と、前記第4 レジスト膜及びその下の前記第3 レジスト膜をマスクと して前記ドレイン端子の上の保護絶縁膜を除去すると共に前記ゲート端子上に残 る絶縁膜を除去する工程とを有し、前記第4レジスト膜及びその下の前記第3レ ジスト膜を残す工程が、前記第4レジスト膜の中にシリコンを含有させて前記第 4レジスト膜をシリコン含有第4レジスト膜とし、前記ドレイン端子上の前記第 3 レジスト膜の除去が、酸素ガス中でのドライエッチング処理により前記シリコ ン含有第4レジスト膜をシリコン酸化膜に変換すると共に、前記ドレイン端子の 上方の開口予定領域に位置する第3レジスト膜を除去することにより行われる、 或いは、

前記チャネル領域を形成する工程の後に、前記TFTのチャネル領域を形成する 際に用いられた前記残存レジストマスクを除去し、続いて、前記ゲート絶縁膜を 覆う保護絶縁膜を堆積させる工程と、前記保護絶縁膜上に第3レジスト膜及び第 4レジスト膜を順に堆積し、前記第3レジスト膜及び前記第4レジスト膜を開口 して前記ゲート端子及び前記ドレイン端子上方に第4レジスト膜の開口部が第3 レジスト膜の開口部を包含する形に形成する工程と、前記第3レジスト膜及び前 記第4レジスト膜をマスクとして前記ゲート端子上の保護絶縁膜及びゲート絶縁 膜、前記ドレイン端子上の保護絶縁膜をそれぞれ除去してコンタクトホールを形 成する工程と、前記第4レジスト膜の開口部に露出している第3レジスト膜をエ ッチング除去すると共に、前記第4レジスト膜及びその下の第3レジスト膜を残 す工程と、前記第4レジスト膜及びその下の第3レジスト膜を残 トホールを覆って上層金属膜を堆積させる工程と、前記第4レジスト膜及びその 下の第3レジスト膜を除去して前記第4レジスト膜及びその下の第3レジスト膜

出証特2001-3082580

特2001-058138

の上の前記上層金属膜を除去し前記コンタクトホールを覆う上部電極を形成する 工程とを有し、前記第4レジスト膜及びその下の第3レジスト膜を形成する工程 が、前記第4レジスト膜の中にシリコンを含有させて前記第4レジスト膜をシリ コン含有第4レジスト膜とし、前記第4レジスト膜の開口部に露出している第3 レジスト膜の除去が、酸素を含む混合ガス中でのドライエッチング処理により前 記シリコン含有第4レジスト膜をシリコン酸化膜に変換すると共に、前記シリコ ン酸化膜に覆われない第3レジスト膜を除去することにより行われる、という適 用形態を採り得る。

[0027]

上記適用形態は、前記保護絶縁膜上に第3レジスト膜及び第4レジスト膜を順 に堆積する工程において、前記第4レジスト膜の少なくとも一部が、前記第3レ ジスト膜よりもエッチング耐性のあるレジスト膜として堆積され、前記第4レジ スト膜及びその下の前記第3レジスト膜を残す工程において、前記第4レジスト 膜の少なくとも一部が、前記第3レジスト膜よりもエッチング耐性のある改質レ ジスト膜とされた後に、前記第4レジスト膜に覆われない第3レジスト膜をエッ チング除去することにより行われ、前記改質レジスト膜の形成が、前記第4レジ スト膜の中にシリコンを含有させて前記第4レジスト膜の少なくとも一部をシリ コン含有第4レジスト膜とし、少なくとも酸素を含む混合ガス中でのドライエッ チング処理により前記シリコン含有第4レジスト膜をシリコン酸化膜に変換する と共に、前記第4レジスト膜に覆われない第3レジスト膜を除去することにより 行われる。

[0028]

【発明の実施の形態】

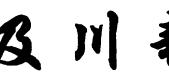

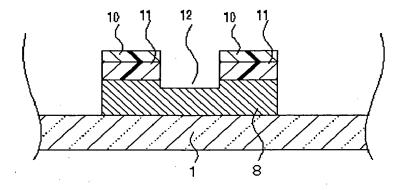

次に、本発明のパターン形成方法の第1の実施形態について図1、2を参照して説明する。図1、2はその製造工程の断面図である。

[0029]

図1(a)に示すように、絶縁基板1上に被エッチング膜2を堆積させ、膜厚 500nm程度のポジ形の第1レジスト膜3を公知のフォトリソグラフィ技術で 形成する。さらに、この第1レジスト膜3上に第2レジスト膜4を形成する。

1 - 7

[0030]

次に、例えば、遮光部と半透光部を有するレチクルをマスクにして、レジスト 膜を露光、現像して、図1(b)に示すように、第1レジスト膜3を半透光部に 対応するレジスト凹部5を有するレジストマスク6とし、第2レジスト膜4をレ ジスト凹部5を挟む形状のレジストマスク7とする。

[0031]

次に、図1(c)に示すように、レジストマスク6及びレジストマスク7をマ スクとして被エッチング膜2をエッチングし、被エッチング膜2からなるアイラ ンド8を形成する。

[0032]

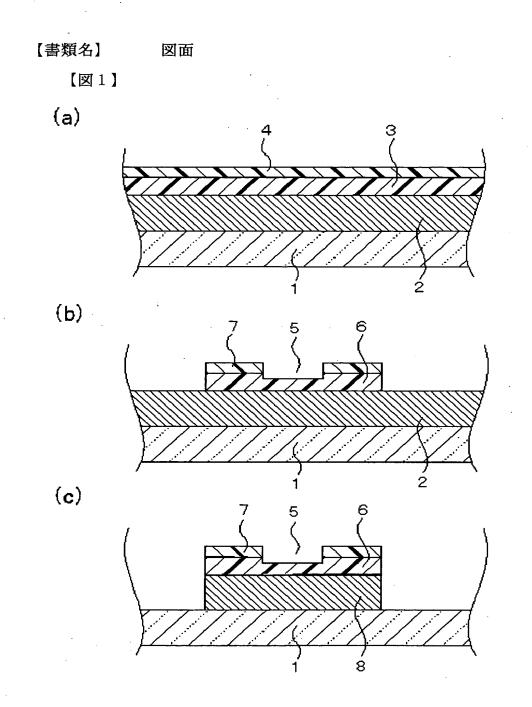

次に、図2(a)に示すように、レジストマスク6及びレジストマスク7をシ ラザン等のシリル化剤に浸漬し、上記レジストマスク7のみをシリル化し、シリ ル化膜9を形成する。このシリル化膜9にはシリコン原子が多量に含まれる。こ こで、レジストマスク6表面はシリル化されない。第1レジスト膜3はシリル化 しないレジスト膜であるからである。

[0033]

ここで、上記のような性質を有する第1レジスト膜及び第2レジスト膜につき 、具体的な材料を以下に挙げる。

【0034】

まず、第1レジスト膜には、シリル化剤と反応するフェノール性水酸基を含有 しない、例えばゴム系の有機材料を選定する。

[0035]

次に、第2レジスト膜には、ノボラック樹脂、またはポリビニルフェノールで 形成し、それらに含まれるフェノール性水酸基をシリル化剤と反応させて、その 表面にシロキサン、ポリシロキサン、ポリシラン、ポリシリーン、カルボシラン を形成する。

[0036]

次に、図2(a)の状態でO2ガス中での異方性のドライエッチングであるR IEを行う。第1レジスト膜の膜厚が500nmの時、ドライエッチング条件と

して、圧力10Pa、ガス流量O<sub>2</sub>=400sccm、RFパワー=1500W 、30秒の処理条件を用いる。

[0037]

ここで使用するガス、及び以後の記述の異方性のドライエッチングであるRI Eで使用するガスの例としてO<sub>2</sub>ガスのみを記述するが、どの場合も使用可能な ガスとして酸素のみ、又は酸素を含む混合ガスである、O<sub>2</sub>ガスと不活性ガス、 例えばO<sub>2</sub>/He、O<sub>2</sub>/Arの混合ガス、又はO<sub>2</sub>ガスとフッ素系ガス、例えば O<sub>2</sub>/SF<sub>6</sub>、O<sub>2</sub>/CF<sub>4</sub>、O<sub>2</sub>/CHF<sub>3</sub>の混合ガスのいずれかのガスでも可能で ある。

[0038]

このRIEで図2(b)に示すように、シリル化膜9を酸化し、シリカ膜10 に変換させる。このシリカ膜10は、シリル化膜9に含まれるシリコンが酸素と 反応しシリコン酸化膜となったものである。そして、同時にレジスト凹部5のレ ジスト膜を無くし、アイランド8を露出させる。ここで、図2(a)で示したレ ジストマスク6は図2(b)に示すようなレジストマスク11に変わる。

[0039]

次に、シリカ膜10とレジストマスク11をエッチングマスクにし、RIEで アイランド8の露出した領域をドライエッチングする。そして、図2(c)に示 すようにアイランド8に凹部12を形成する。

[0040]

最後に、シリカ膜10とレジストマスク11を除去する。このようにして、凹 部12を有するアイランド8が形成される。

[0041]

以上のように、本実施形態では、図1(b)から図1(c)に到る工程で1回 目のエッチングを行い、図2(a)から図2(b)に到る工程で2回目以降のエ ッチングを行うのであるが、2回目以降のエッチングのマスクにされるシリカ膜 10は、レジスト凹部5のレジスト膜をエッチング除去する際に形成され、しか も、O<sub>2</sub>ガス中での異方性のRIEにより、シリル化膜9を酸化し、O<sub>2</sub>ガス系の プラズマエッチングの影響を受けにくいシリカ膜10に変換することにより形成

されるので、シリカ膜10の平面形状はO2ガス中でのRIEを行う前のレジス トマスク7の平面形状に近い形状を維持することが出来る。従って、レジストマ スク11の形成も容易になりその平面形状制御性が向上するので、凹部12の形 状を設計値に近い形状とすることが出来る。

[0042]

また、本実施形態のように、第2レジスト膜としてシリル化できるレジスト膜 を用いている場合には、必ずしも第1レジスト膜にレジスト凹部5を形成する必 要はなく、レジスト凹部5のないレジストマスク6を形成し、シリル化膜9をマ スクにO2ガスによるRIEでレジストマスク11を形成することもできる。こ の場合には、レチクルに半透光部は必要とならない。

[0043]

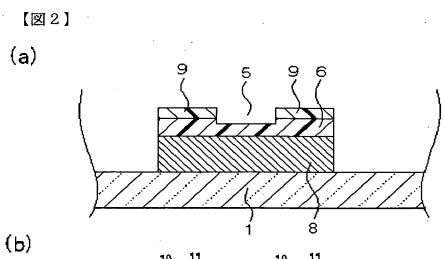

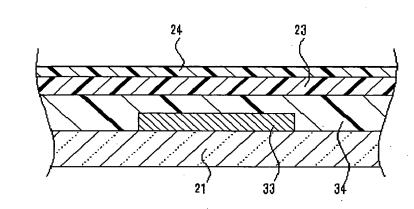

次に、本発明のパターン形成方法の第2の実施形態について図3、4を参照し て説明する。図3、4はその製造工程の断面図である。

[0044]

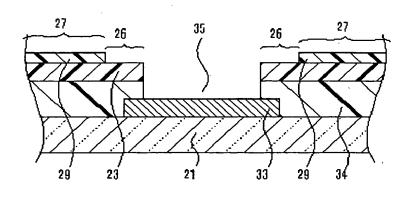

図3(a)に示すように、絶縁基板21上に下層配線33を形成し、下層配線 33を覆って絶縁膜34を堆積させる。

[0045]

次に、絶縁膜34の上に、膜厚500nm程度のポジ形の第1レジスト膜23 を公知のフォトリソグラフィ技術で形成する。さらに、この第1レジスト膜23 上に第2レジスト膜24を形成する。ここで、第2レジスト膜24はポジ形のシ リル化が可能なレジスト膜であり、その膜厚は300nm程度である。

[0046]

次に、例えば、遮光部と半透光部を有するレチクルをマスクにして、レジスト 膜を露光、現像して、図3(b)に示すように、第1レジスト膜23及び第2レ ジスト膜24を透光部に対応する開口部25、半透光部に対応する薄レジストマ スク26、遮光部に対応する厚レジストマスク27とする。

[0047]

次に、図3(c)に示すように、薄レジストマスク26及び厚レジストマスク 27をマスクとして絶縁膜34をエッチングし、絶縁膜34に下層配線33の上

出証特2001-3082580

に位置するコンタクトホール35を形成する。

[0048]

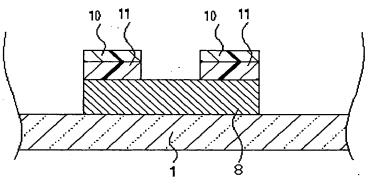

次に、図4(a)に示すように、薄レジストマスク26及び厚レジストマスク 27をシラザン等のシリル化剤に浸漬し、厚レジストマスク27のうち第2レジ スト膜24のみをシリル化し、シリル化膜29を形成する。このシリル化膜29 にはシリコン原子が多量に含まれる。ここで、薄レジストマスク26表面はシリ ル化されない。薄レジストマスク26はシリル化しない第1レジスト膜23によ り構成されているからである。

[0049]

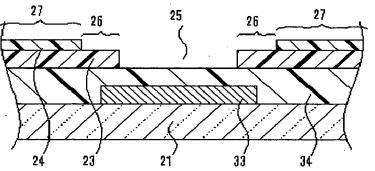

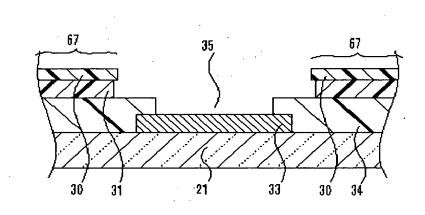

次に、O2ガス中での異方性のRIEを行う。このRIEで、図4(b)に示 すように、シリル化膜29を酸化し、シリカ膜30に変換させる。このシリカ膜 30は、シリル化膜29に含まれるシリコンが酸素と反応しシリコン酸化膜とな ったものである。そして、薄レジストマスク26及び厚レジストマスク27を一 様にエッチングして薄レジストマスク26を除去してしまい、厚レジストマスク 27を残存レジストマスク67とする。ここで、図4(a)で示した厚レジスト マスク27を構成する第1レジスト膜23及びシリル化膜29はそれぞれレジス トマスク31及びシリカ膜30となり、シリカ膜30がレジストマスク31に対 してオーバーハング状に形成される。

[0050]

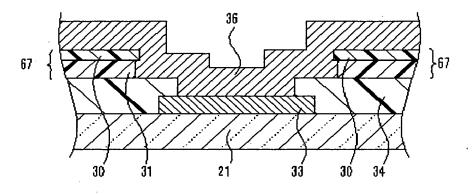

次に、図5(a)に示すように、コンタクトホール35の形成された絶縁膜3 4とシリカ膜30、レジストマスク31を覆って上層金属膜36を堆積させる。

【0051】

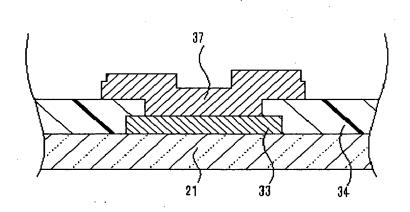

次に、シリカ膜30及びレジストマスク31を除去すると、図5(b)に示す ように、その上の上層金属膜36も除去され、コンタクトホール35を通して下 層配線35と上層配線37が接続される。

[0052]

以上のように、本実施形態では、図3(b)から図3(c)に到る工程で1回 目のエッチングを行い、図4(a)から図4(b)に到る工程で2回目のエッチ ングを行うのであるが、2回目のエッチングのマスクにされるシリカ膜30は、 薄レジストマスク26をエッチング除去する際に形成され、しかも、O<sub>2</sub>ガス中 での異方性のRIEにより、シリル化膜29を酸化し、O<sub>2</sub>ガス系のプラズマエ ッチングの影響を受けにくいシリカ膜30に変換することにより形成されるので 、シリカ膜30の平面形状はO<sub>2</sub>ガス中でのRIEを行う前の厚レジストマスク 27を構成する第2レジスト膜24の平面形状に近い形状を維持し、かつ、シリ カ膜30の下のレジストマスク31をその内側に形成することが出来、リフトオ フし易いレジスト構造を実現できる。従って、上層配線37の平面形状制御性が 向上するので、上層配線間の短絡の確率を大幅に減らすことが可能となる。

[0053]

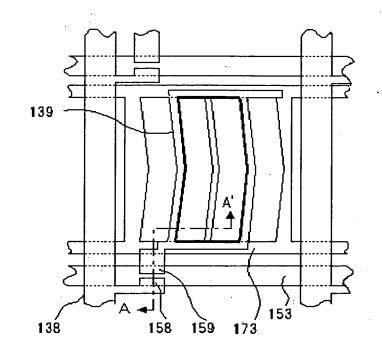

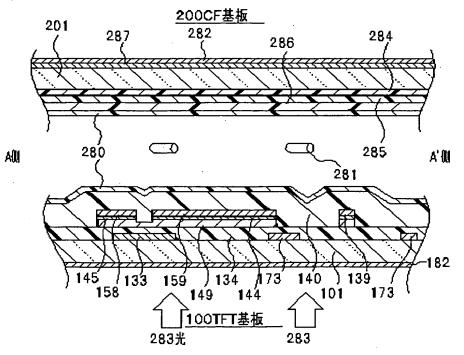

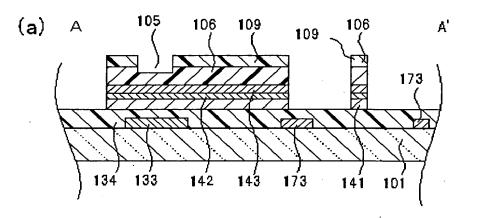

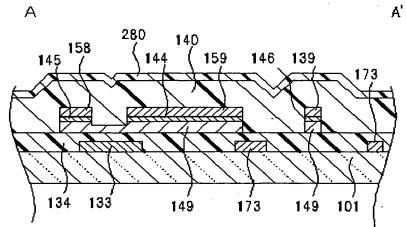

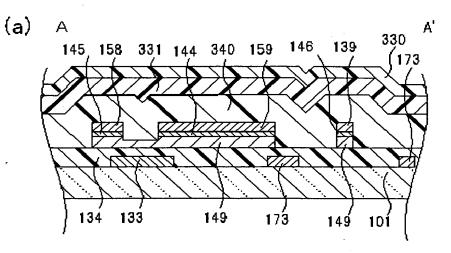

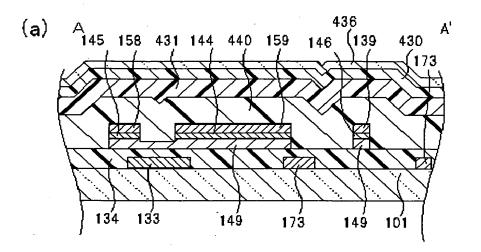

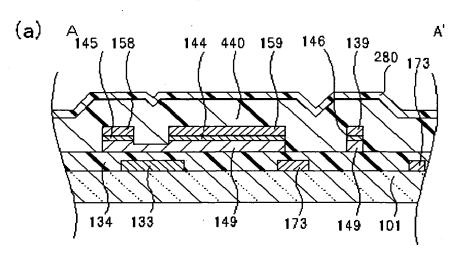

次に、本発明のパターン形成方法の第1の実施形態を横電界型の液晶表示装置 に適用した第1の例を本発明の第3の実施形態として図6~14を参照して説明 する。図6は、1画素分の表示セルについて、TFT基板の様子を示すもので、 図6(a)は、TFT基板をその上面から眺めたときの平面図であり、図6(b) )は、図6(a)における切断線A-A'を通りTFT基板に直交する平面でT FT基板、液晶、CF基板(TFT基板に対向するカラーフィルタ基板を指し、 以下、CF基板と記載する)を切断したときの断面図である。また、図7~14 は、横電界型の液晶表示装置のTFT基板の製造方法を工程順に示す製造工程断 面図であり、各図において(a)は図6(a)の切断線A-A'に沿った断面図 であり、(b)、(c)は図6(a)には示されないが、それぞれゲート配線の 外部取出し用端子としてのゲート端子、ドレイン配線の外部取出し用端子として のドレイン端子の断面図である。

【0054】

横電界型の液晶表示装置の動作について図6を参照して簡単に説明すると次の ようになる。

【0055】

第1透明基板101の上にはまずゲート電極122を兼ねるゲート配線222 が基板上を並行して配線され、同時に共通電極242も形成される。共通電極2 42は櫛歯状に形成され、後の工程で形成されるやはり櫛歯状の画素電極と対を なして電界を発生させる。ゲート配線222、共通電極242の上にはゲート絶

縁膜123が形成され、その上をドレイン配線232がゲート配線222と交差 するようにして形成される。ドレイン配線232はドレイン電極132を兼ね、 ドレイン配線232の形成と同時にソース電極131及びその延長線である櫛歯 状の画素電極157が形成される。ドレイン配線232、ソース電極131、画 素電極157を覆ってパッシベーション膜155が形成されるが、ゲート配線2 22及びドレイン配線232は基板端部においては外部との接続用にその上の絶 縁膜が開口され、図5には示されないが、コンタクトホールが形成され、コンタ クトホールを通して外部からゲート配線222及びドレイン配線232に電気信 号が印加される。

[0056]

画素電極157は、図5(a)に示すように、下方に形成された共通電極24 2と共に互いに平行する電極を形成し、これらの間に電圧を印加することにより 、第1透明基板101の表面に概略平行な電界を生じさせ、第1透明基板101 とそれに対向する基板との間に充填されることとなる液晶218の向きを制御す る。

【0057】

次に、第3の実施形態の横電界型の液晶表示装置の製造方法について図6~1 3を参照して説明する。

[0058]

まず、第1透明基板101の上にCr等のゲート電極133を兼ねるゲート配 線153が基板上を並行して配線され、同時に第1透明基板101の他の領域上 に櫛歯状の共通電極173(及びゲート端子電極193)とが形成される(図6) )。共通電極173は、後の工程で形成される櫛歯状の画素電極と対をなすよう に形成され、それぞれの電極に電圧を印加することにより対向する櫛歯状の電極 間で電界を生じさせる。

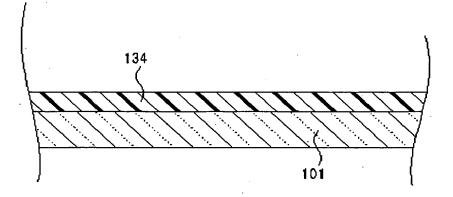

【0059】

次に、シリコン酸化膜及びシリコン窒化膜(SiNx)を順に第1透明基板1

01上全面に堆積してゲート絶縁膜134が形成され、その上をドレイン配線1

53がゲート配線153と交差するようにして形成される。ドレイン配線138

出証特2001-3082580

はドレイン電極158を兼ね、ドレイン配線138の形成と同時にソース電極1 59及びその延長線である櫛歯状の画素電極139が形成される。ドレイン配線 138、ソース電極159、画素電極139を覆ってパッシベーション膜140 が形成されるが、ゲート配線153及びドレイン配線138は基板端部において は外部との接続用にその上の絶縁膜が開口され、図6には示されないが、コンタ クトホールを通して外部からゲート配線153及びドレイン配線138に電気信 号が印加される。

[0060]

画素電極139は、図6(a)に示すように、その下方に形成された共通電極 173と共に互いに並行する電極を形成し、これらの間に電圧を印加することに より、第1透明基板101の表面に概略平行な電界を生じさせ、第1透明基板1 01とそれに対向する基板との間に充填されることとなる液晶281の向きを制 御する。

[0061]

次に、第3の実施形態の横電界型の液晶表示装置の製造方法について、図7~ 14を参照して説明する。

[0062]

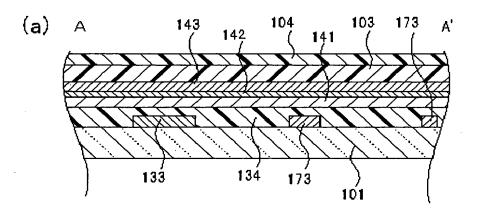

まず、第1透明基板101の上にCr等のゲート電極133を形成するが、こ のとき同時に第1透明基板101の他の領域上に櫛歯状の共通電極173及びゲ ート端子電極193とを形成する(図7)。

[0063]

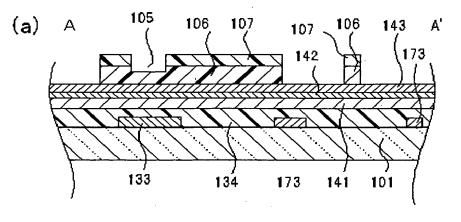

次に、シリコン酸化膜及びシリコン窒化膜(SiNx)を順に第1透明基板1 01上全面に堆積してゲート絶縁膜134とし、続いて、a-Si膜141、n <sup>+</sup>型a-Si膜142、ソース・ドレイン用のCr等の金属膜143を順に堆積 し

、さらに金属膜143の上に膜厚500nm程度のポジ形の第1レジスト膜10 3及び第2レジスト膜104を順次形成する。ここで、第2レジスト膜104は ポジ形のシリル化が可能なレジスト膜であり、その膜厚は300nm程度である

[0064]

次に、例えば、遮光部と半透光部を有するレチクルをマスクにして、レジスト 膜を露光、現像して、図8に示すように、ゲート電極133上方に、第1レジス ト膜103を半透光部に対応するレジスト凹部105を有するレジストマスク1 06とし、第2レジスト膜104をレジスト凹部105を挟む形状のレジストマ スク107とする。このとき、櫛歯状の共通電極173に挟まれて形成されるや はり櫛歯状の画素電極が形成されるべき領域とドレイン端子電極が形成されるべ き領域には、レジストマスク106及びレジストマスク107が重ねて形成され る。

[0065]

次に、図9に示すように、レジストマスク106及びレジストマスク107を マスクとして金属膜143、 $n^+$ 型a-Si膜142、a-Si膜141を上か ら順にエッチング除去する。

[0066]

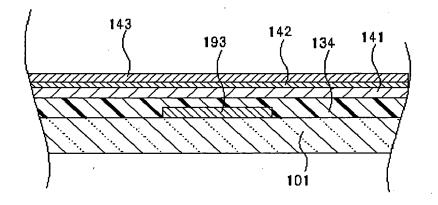

次に、レジストマスク106及びレジストマスク107をシラザン等のシリル 化剤に浸漬し,上記レジストマスク107のみをシリル化し、シリル化膜109 を形成する。このシリル化膜109にはシリコン原子が多量に含まれる。ここで 、レジストマスク106表面はシリル化されない。第1レジスト膜103はシリ ル化しないレジスト膜であるからである。

[0067]

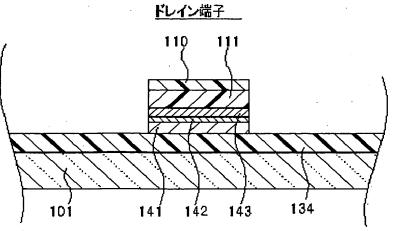

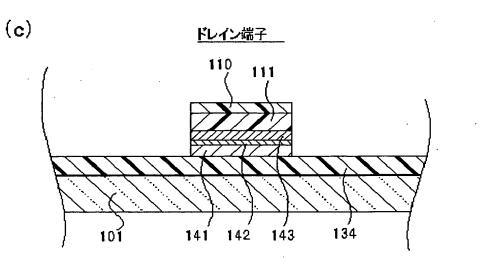

次にO<sub>2</sub>ガス中での異方性のRIEを行う。このRIEで、図10に示すよう に

、シリル化膜109を酸化し、シリカ膜110に変換させる。このシリカ膜11 0は、シリル化膜109に含まれるシリコンが酸素と反応しシリコン酸化膜とな ったものである。そして、レジスト凹部105のレジスト膜を除去し、その下に 位置する金属膜143を露出させる。ここで、図9で示したレジストマスク10 6は図10に示すようなレジストマスク111に変わる。

[0068]

次に、シリカ膜110とレジストマスク111をエッチングマスクにし、SF

出証特2001-3082580

特2001-058138

6、HC1とHeの混合ガスを反応ガスとするRIEで金属膜143の露出した 領域をドライエッチングし、さらにエッチングを進めてn<sup>+</sup>型a-Si膜142 の全部とa-Si膜141の一部をエッチング除去する。そして、図11に示す ようにa-Si膜141に凹部112を形成する。この場合のドライエッチング 条件として、圧力30Pa、ガス流量SF<sub>6</sub>/HC1/He=50/100/2 00sccm、RFパワー=800W、60秒の処理条件を用いる。

[0069]

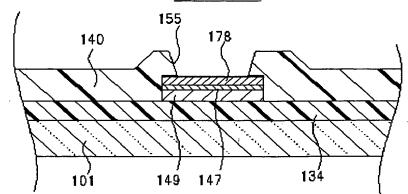

次に、シリカ膜110とレジストマスク111を除去すると、図12に示すよ うに、ソース電極159、オーミック層144とドレイン電極158、オーミッ ク層145、凹部112を有するTFTのアイランド108、画素電極139、 ドレイン端子電極178、オーミック層147が形成される。

[0070]

ここで、上記実施形態では、図8において、レジストマスク106及びレジス トマスク107をマスクとして金属膜143、 $n^+$ 型a-Si膜142、a-Si 膜141を上から順に一度にエッチング除去したが、金属膜143のみをエッ チング除去し、続いて、O<sub>2</sub>ガス中での異方性のRIEを行って、図9に示すよ うに

、シリル化膜109をシリカ膜110に変換させ、その後、レジスト凹部105 のレジスト膜をエッチング除去すると同時に $n^+$ 型a-Si膜142、a-Si膜141を上から順にエッチング除去し、さらにエッチングを進めてレジスト凹 部105下方の $n^+$ 型a-Si膜142の全部及びa-Si膜141の一部を除 去する方法も可能である。この場合、エッチング条件としてはゲート絶縁膜13 4 $2n^+$ 型a-Si膜142、a-Si膜141との選択比の大きい条件が選ば れる。

[0071]

以上のように、本実施形態では、図8から図9に到る工程で1回目のエッチン グを行い、図9から図11に到る工程で2回目のエッチングを行うのであるが、 2回目のエッチングのマスクにされるシリカ膜110は、レジスト凹部105の レジスト膜をエッチング除去する際に形成され、しかも、O<sub>9</sub>ガス中での異方性

出証特2001-3082580

のRIEにより、シリル化膜109を酸化し、O2ガス系のプラズマエッチング の影響を受けにくいシリカ膜110に変換することにより形成されるので、シリ カ膜110の平面形状はO2ガス中でのRIEを行う前のレジストマスク107 の平面形状に近い形状を維持することが出来る。従って、レジストマスク111 の形成も容易になりその平面形状制御性が向上するので、凹部112の形状を設 計値に近い形状とすることが出来る。また、シリカ膜110及びレジストマスク 111をマスクとして2回のエッチングに晒される画素電極139及びドレイン 端子電極178は、パターン精度の良いシリカ膜110及びレジストマスク11 1をマスクとしているので設計値通りのパターンに形成することができる。

[0072]

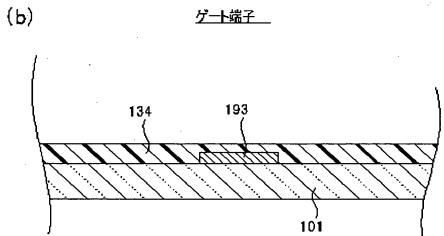

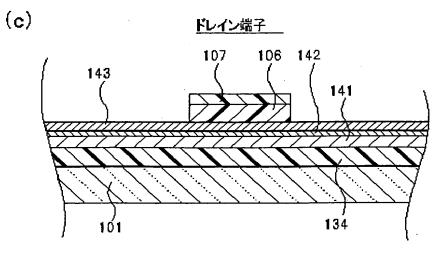

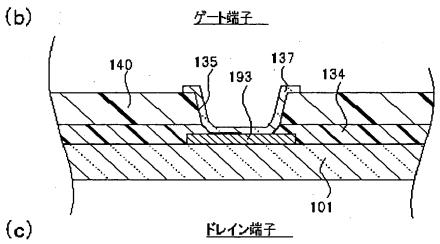

次に、パッシベーション膜140を成膜後、フォトリソグラフィ工程とSF<sub>6</sub> /Heガス=50/150sccm、10Pa、1000W、250秒のドライ エッチング処理によりゲート端子及びドレイン端子において、ゲート端子電極1 93及びドレイン端子電極178の上にそれぞれコンタクトホール135、15 5を形成する。ここで、ゲート端子では、コンタクトホール135はゲート絶縁 膜134及びパッシベーション膜140を貫通し、ドレイン端子では、コンタク トホール155はパッシベーション膜140のみを貫通する構成となる(図13)。

[0073]

次に、コンタクトホール135、155を覆うようにしてITO等からなる透 明金属膜を成膜後、フォトリソグラフィ工程と塩化第2鉄系エッチング液により ゲート端子透明電極137及びドレイン端子透明電極157を形成し、端子部に おける配線引出抵抗を下げ、その上で端子領域を除く表示部の表面を配向膜28 0で覆う(図14)。

【0074】

最後に、第1透明基板101の裏面(TFTの形成されていない第1透明基板 101の面を裏面と呼ぶ)に偏光板182を形成すると、横電界型の液晶表示装 置のTFT基板が完成する(図6)。

[0075]

液晶表示装置の色表示は、図6(b)に示すように、第1透明基板101の裏 面から光283を入射させてTFT基板100に対向するカラーフィルタ(以降 、CFと略記する)基板200を照射することにより行われる。

[0076]

一方、CF基板200は次のようにして形成される。

[0077]

まず、ガラス等の透明絶縁材料からなる第2透明基板201及び第2透明基板 201の一方の面上のブラックマトリクス284、色層285、シリコン窒化膜 (SiNx)等からなる第2絶縁膜286と、第2透明基板201の他方の面上 の導電膜287、偏光板282とを備え、基板の最上層の表面にオフセット印刷 等による方法で配向膜280を印刷することにより形成される。

[0078]

こうして得られたTFT基板100とCF基板200の配向膜をラビング処理 し、所定の方向に配向膜分子を並べ、この2枚の基板が所定の間隔を持つように セルギャップ材を挟みこませて組み合わせ、その間隙に液晶281を封止する。

[0079]

また、TFT基板100の表面に対して実効的に横方向の電界を発生させる櫛 歯状の画素電極139と共通電極173との相互間隔は、およそ7μmが設定さ れる。

【0080】

また、偏光板182、偏光板282はおよそ0.2mmの厚さに設定される。 導電膜287は、およそ50nmの厚さに設定される。第1透明基板及び第2透 明基板は、およそ0.7mmの厚さに設定される。ブラックマトリクス284は 、およそ1 $\mu$ mの厚さに設定される。色層285は、およそ1 $\mu$ mの厚さに設定 される。第2絶縁膜286の厚さはおよそ1 $\mu$ mの厚さに設定される。配向膜2 80は、およそ50nmの厚さに設定される。ゲート絶縁膜134は、およそ5 00nmの厚さに設定される。パッシベーション膜140は、およそ300nm の厚さに設定される。共通電極173は、およそ400nmの厚さに設定される 。また、液晶281の厚さ(セルギャップ)は、セル内スペーサを適度な散布密

出証特2001-3082580

度にて配置し、4.5µmと設定される。

[0081]

このようにして得られた液晶パネルは、ラビング方法により規定した液晶の配 向方向にTFT基板100の偏光板182の透過軸を一致させ、かつ、CF基板 200にはTFT基板100側と吸収軸を直交させた偏光板282を貼り合わせ 、光283をTFT基板100側から照射し、画素電極139と共通電極173 の間に自在に電位差を与えることで、黒表示から白表示までフルカラー表示を行 うことができる。

[0082]

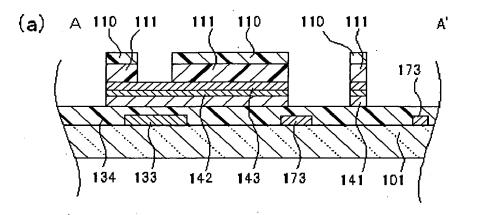

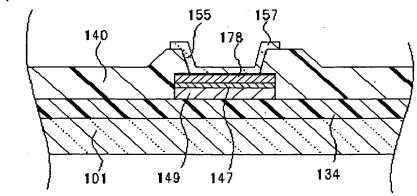

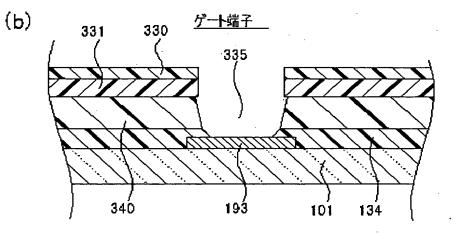

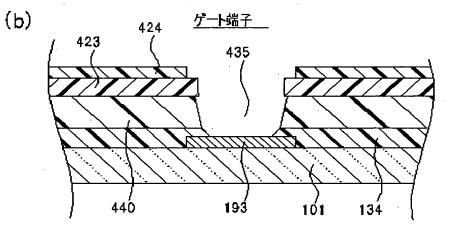

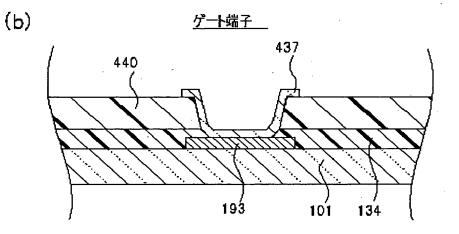

次に、本発明のパターン形成方法の第1の実施形態を横電界型の液晶表示装置 に適用した第2の例を本発明の第4の実施形態として図15~18を参照して説 明する。第2の例が上述した第1の例と異なるのは、本発明のパターン形成方法 の第1の実施形態をコンタクトホール形成工程に用いた点である。従って、本実 施形態は第1の例と第2の例とを同時に横電界型の液晶表示装置の製造工程に適 用しており、液晶表示装置の製造工程に一層の工程短縮効果及び歩留まり向上効 果が得られる。勿論、第1の例と第2の例のいずれかを横電界型の液晶表示装置 に用いることも可能である。

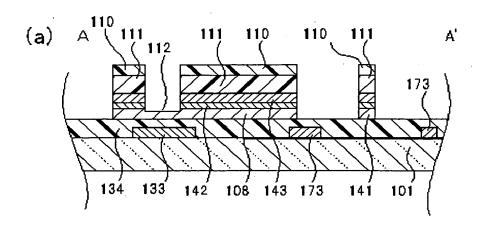

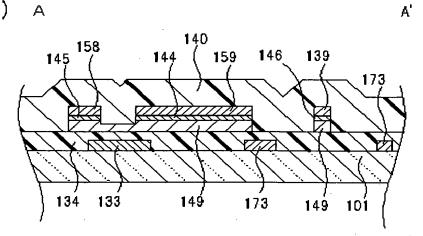

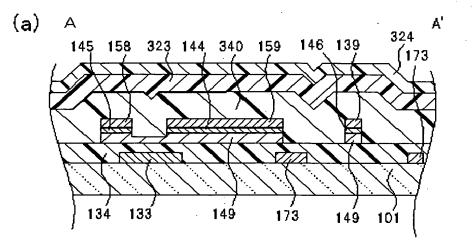

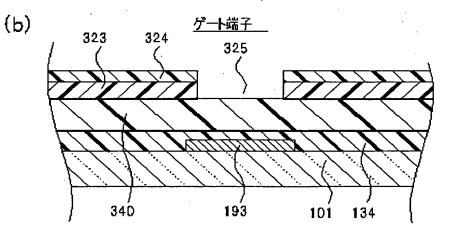

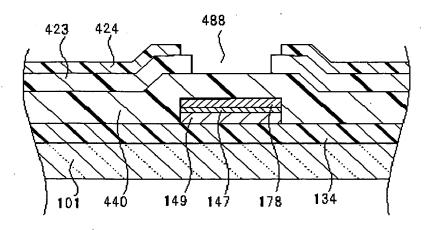

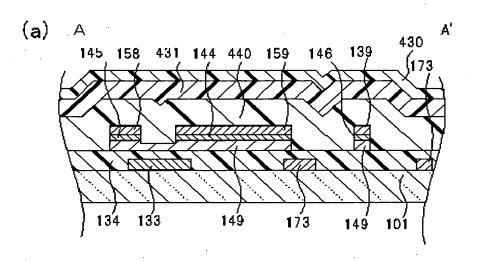

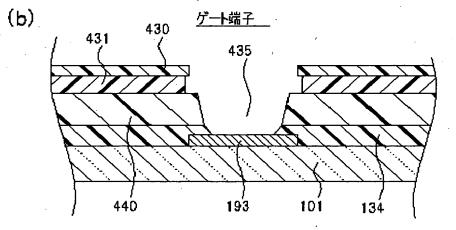

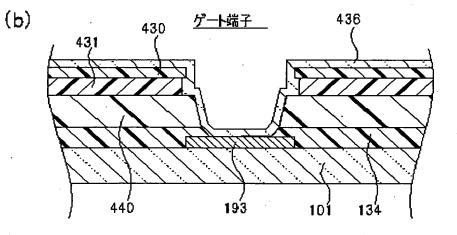

[0083]

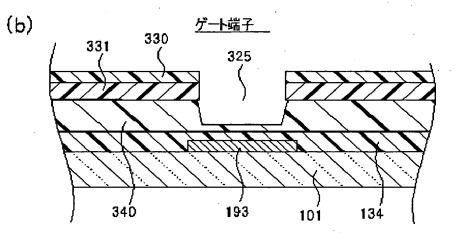

また、本実施形態においても、図15~18は、横電界型の液晶表示装置のT FT基板の製造方法を工程順に示す製造工程断面図であり、各図において(a) は図6(a)の切断線A-A'に沿った断面図であり、(b)、(c)は図6( a)には示されないが、それぞれゲート配線の外部取出し用端子としてのゲート 端子、ドレイン配線の外部取出し用端子としてのドレイン端子の断面図である 。本実施形態の製造工程のソース電極、ドレイン電極形成までは、第3の実施形 態の図7~12までと同様であるので説明は省略し、ソース電極、ドレイン電極 の上にパッシベーション膜を形成する工程以降について説明することとする。

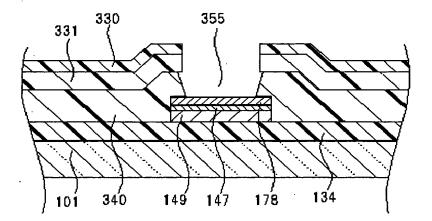

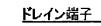

[0084]

まず、図12の状態から、パッシベーション膜340を成膜後、パッシベーション膜340の上に膜厚500nm程度のポジ形の第1レジスト膜323及びポ

ジ形のシリル化が可能な第2レジスト膜324を膜厚300nm程度に形成する

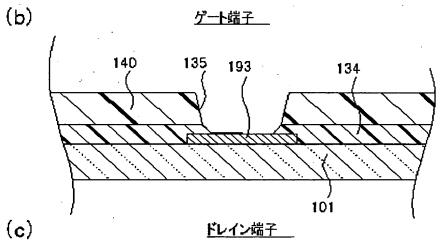

[0085]

次に、例えば、遮光部と半透光部を有するレチクルをマスクにして、レジスト 膜を露光、現像して、ゲート端子電極193上方に、透光部に対応する開口部3 25を、ドレイン端子電極178上方に、半透光部に対応する第2レジスト膜3 24のみが開口された開口部388を形成し、残りの領域は第1レジスト膜32 3及び第2レジスト膜324で覆う(図15)。

[0086]

次に、第1レジスト膜323及び第2レジスト膜324をシラザン等のシリル 化剤に浸漬し、第2レジスト膜324のみをシリル化し、シリル化膜とする。こ のシリル化膜にはシリコン原子が多量に含まれる。ここで、第1レジスト膜32 3はシリル化されない。第1レジスト膜323はシリル化しないレジスト膜であ るからである。

[0087]

次に、O2ガス中での異方性のRIEを行う。このRIEで、シリル化膜を酸 化し、シリカ膜330に変換させる。このシリカ膜330は、シリル化膜に含ま れるシリコンが酸素と反応しシリコン酸化膜となったものである。そして、RI Eを続けながらドレイン端子電極178上方の第1レジスト膜323を除去し、 同時にゲート端子電極193上方のパッシベーション膜340を一部除去する。 このとき、パッシベーション膜340よりもその下のゲート絶縁膜134の方が 厚い場合は、パッシベーション膜340を全て除去してゲート絶縁膜134の一 部を除去するまでエッチングしても良い。この工程により、図15で示した第1 レジスト膜323は図16に示すようなレジストマスク331に変わる(図16 )。

[0088]

次に、シリカ膜330とレジストマスク331をエッチングマスクにし、 SF<sub>6</sub>とHeの混合ガスを反応ガスとするRIEでドレイン端子電極178上方 及びゲート端子電極193上方の絶縁膜を全て除去すると、ドレイン端子電極1

30.

78及びゲート端子電極193上にコンタクトホール355及びコンタクトホール335がそれぞれ形成される(図17)。この場合のドライエッチング条件として、SF<sub>6</sub>/Heガス=50/150sccm、10Pa、1000W、25 0秒のドライエッチング処理条件を用いる。

[0089]

本実施形態では、図15から図16に到る工程でドレイン端子電極178上方 の第1レジスト膜323を除去しながらゲート端子電極193上方のパッシベー ション膜340を一部除去しているが、まずゲート端子電極193上方のパッシ ベーション膜340のみを選択的に一部除去した後に第2レジスト膜324をシ リカ膜にしつつドレイン端子電極178上方の第1レジスト膜323を除去して ドレイン端子電極178上方及びゲート端子電極193上方の絶縁膜の膜厚をほ ぼ等しくした後に、ドレイン端子電極178上方及びゲート端子電極193上方 の絶縁膜を除去しても良い。この方法は、特にパッシベーション膜の方がゲート 絶縁膜よりも厚く形成されている場合に有効である。

[0090]

この後は、第3の実施形態の図14以降の製造方法により横電界型の液晶表示 装置が完成する。

[0091]

以上のように、本実施形態では、図16の工程で1回目のエッチングを行い、 図16から図17に到る工程で2回目のエッチングを行うのであるが、2回目の エッチングのマスクにされるシリカ膜330は、第1レジスト膜323をエッチ ング除去する際に形成され、しかも、O2ガス中での異方性のRIEにより、シ リル化膜を酸化し、O2ガス系のプラズマエッチングの影響を受けにくいシリカ 膜330に変換することにより形成されるので、シリカ膜330の平面形状はO 2ガス中でのRIEを行う前の第2レジスト膜324の平面形状に近い形状を維 持することが出来る。従って、レジストマスク331の形成も容易になりその平 面形状制御性が向上するので、ゲート端子電極193及びドレイン端子電極17 8上のコンタクトホール335、355の形状を設計通りの形状とすることが出 来る。

[0092]

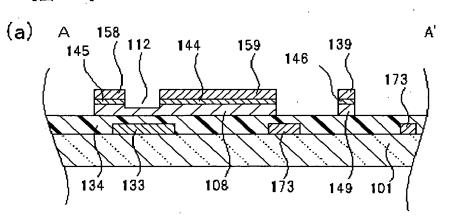

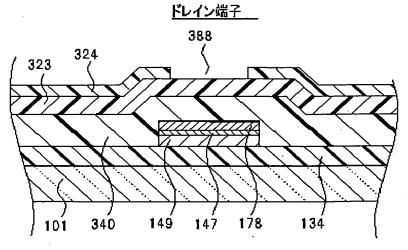

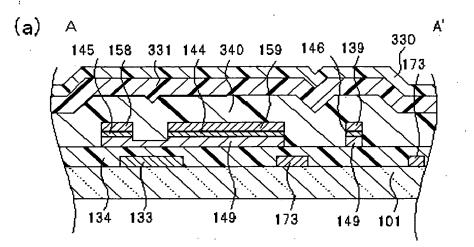

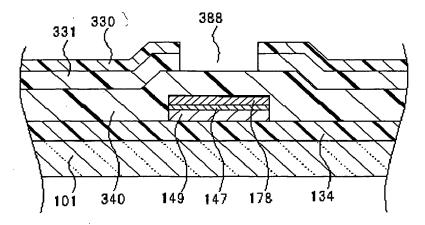

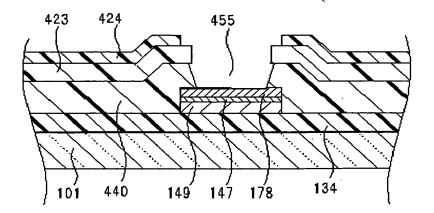

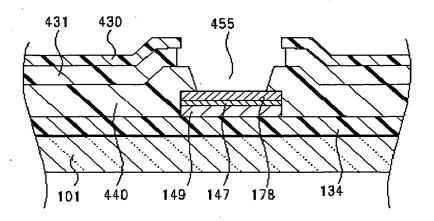

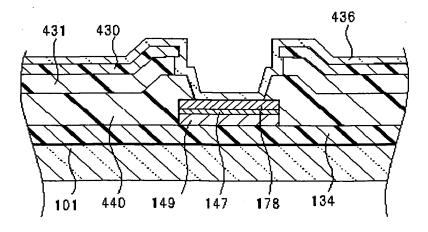

次に、本発明のパターン形成方法の第2の実施形態を横電界型の液晶表示装置 に適用した例を本発明の第5の実施形態として図18~22を参照して説明する 。本実施形態は、上述した第3の実施形態とは、コンタクトホール及びその後に 続くゲート端子透明電極及びドレイン端子透明電極の形成方法が異なる。従って 、第3の実施形態と本実施形態とを同時に横電界型の液晶表示装置の製造工程に 適用すれば液晶表示装置の製造工程に一層の工程短縮効果及び歩留まり向上効果 が得られることは言うまでもない。また、本実施形態においても、図18~22 は、横電界型の液晶表示装置のTFT基板の製造方法を工程順に示す製造工程断 面図であり、各図において(a)は図6(a)の切断線A-A'に沿った断面図 であり、(b)、(c)は図6(a)には示されないが、それぞれゲート配線の 外部取出し用端子としてのゲート端子、ドレイン配線の外部取出し用端子として のドレイン端子の断面図である。本実施形態の製造工程のソース電極、ドレイン 電極形成までは、第3の実施形態の図7~12までと同様であるので説明は省略 し、ソース電極、ドレイン電極の上にパッシベーション膜を形成する工程以降に ついて説明することとする。

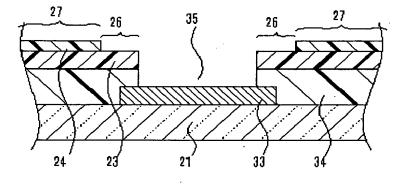

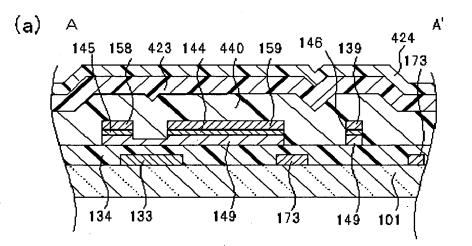

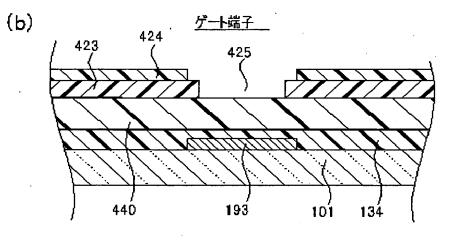

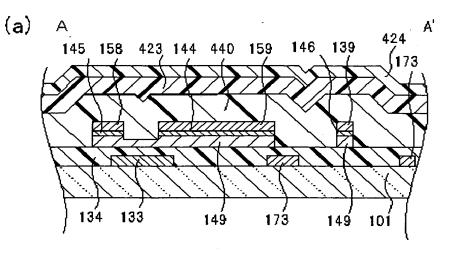

[0093]

まず、図12の状態からパッシベーション膜440を成膜後、パッシベーショ ン膜440の上に膜厚500nm程度のポジ形の第1レジスト膜423及びポジ 形のシリル化が可能な第2レジスト膜424を膜厚300nm程度に形成し、続 いて、例えば、遮光部と半透光部を有するレチクルをマスクにして、レジスト膜 を露光、現像して、ゲート端子電極193及びドレイン端子電極178上方に、 透光部に対応するそれぞれ開口部425、488を第1レジスト膜423に開口 し、開口部425、488の近傍以外の領域に遮光部に対応する第2レジスト膜 424を形成する(図18)。

【0094】

次に、第1レジスト膜423及び第2レジスト膜424をマスクとして開口部 425に露出しているパッシベーション膜440及びゲート絶縁膜134と開口 部488に露出しているパッシベーション膜440をエッチング除去してゲート

出証特2001-3082580

端子電極193及びドレイン端子電極178の表面を露出させ、それぞれコンタ クトホール435、455を形成する(図19)。

[0095]

次に、第1レジスト膜423及び第2レジスト膜424をシラザン等のシリル 化剤に浸漬し、第2レジスト膜424のみをシリル化し、シリル化膜とする。こ のシリル化膜にはシリコン原子が多量に含まれる。ここで、第1レジスト膜42 3表面はシリル化されない。第1レジスト膜423はシリル化しないレジスト膜 であるからである。

[0096]

次に、O<sub>2</sub>ガス中での異方性のRIEを行う。このRIEでシリル化膜を酸化 し

、シリカ膜430に変換させる。このシリカ膜430は、シリル化膜に含まれる シリコンが酸素と反応しシリコン酸化膜となったものである。そして、RIEを 続けながら開口部435、455近傍の第1レジスト膜423を除去し、開口部 435、455近傍のパッシベーション膜440の表面を露出させる。ここで、 図19で示した第1レジスト膜423は図20に示すようなレジストマスク43 1に変わるが、シリカ膜430はエッチング中エッチングがほとんど進行せず、 逆に、第1レジスト膜423はエッチングが進行し易いため、シリカ膜430は レジストマスク431に対してオーバーハング状に形成される(図20)。

[0097]

次に、開口部435、455の形成されたパッシベーション膜440及びシリカ膜430とレジストマスク431を覆って、ITO等からなる透明金属膜43

6を成膜する(図21)。

[0098]

図21の状態からシリカ膜430及びその下のレジストマスク431を除去す ると、シリカ膜430の上の透明金属膜436も一緒に除去され、ゲート端子電 極193及びドレイン端子電極178上の開口部435、455にそれぞれゲー ト端子透明電極437及びドレイン端子透明電極457が形成される。この後は 、第3の実施形態と同様にしてパッシベーション膜440を配向膜280で覆う

工程が続き、横電界型の液晶表示装置が完成する(図22)。

【0099】

以上のように、本実施形態では、図19の工程で1回目のエッチングを行い、 図20の工程で2回目のエッチングを行うのであるが、2回目のエッチングのマ スクにされるシリカ膜430は、第1レジスト膜423をエッチング除去する際 に形成され、しかも、O2ガス中での異方性のRIEにより、シリル化膜を酸化 し

、O2ガス系のプラズマエッチングの影響を受けにくいシリカ膜430に変換す ることにより形成されるので、シリカ膜430の平面形状はO2ガス中でのRI Eを行う前の第2レジスト膜424の平面形状に近い形状を維持することが出来 る。従って、レジストマスク431の形成をシリカ膜430の形状と独立させて 形成でき、シリカ膜430のレジストマスク431に対するオーバーハング形状 を容易に制御することができ、透明金属膜436をリフトオフする際の最適の下 地を形成することが可能となる。

[0100]

以上が本発明の実施形態の説明であるが、本発明は、上記の実施形態に限定さ れることなく、第2レジスト膜は、第1レジスト膜に比較しエッチング耐性のあ るレジスト膜、または別の表現では改質レジスト膜となるように形成されるが、 このエッチング耐性のあるレジストの形成方法として、上述した実施形態では、 上層の第2レジスト膜にシリル化が可能なレジスト膜を用い、第2レジスト膜を シラザンを含むシリル化剤に浸漬しシリル化させ、さらに酸素を含むガスでのド ライエッチングによりシリコン酸化膜に改質して、エッチング耐性を持つように する場合を示したが、これ以外の方法として、(1)当初よりエッチング耐性の あるレジスト膜を塗布形成する場合や、(2)ドライエッチングによりエッチン グ中にエッチング耐性のある膜に改質するレジスト膜を予め選定し、第2レジス ト膜として堆積させておく場合とがあり、以下にそれらを説明する。

(1)当初よりエッチング耐性のあるレジスト膜を塗布形成する場合 第1レジスト膜及び第2レジスト膜を共に有機材料からなるレジスト膜とする場 合で、この場合、ベンゼン環を多く含むほどドライエッチング耐性が上昇し、

出証特2001-3082580

- (a)ノボラック系樹脂(例:クレゾールノボラック樹脂、クレゾールノボ

ラック樹脂とナフトキノンジアジド-5-スルフォン酸エステルを混

合した有機材料)

- (b) 芳香族ビスアジドーゴム系(例:環化ポリイソプレン、環化ポリブタ ジエンにビスアジド化合物を混合した有機材料)

- (c)ケイ皮酸素

- (d) クロルメチル化ポリスチレン

- (e) メチルメタクリレード

- (f) アクリル酸の共重合樹脂系(例:ポリアクリルアミド、ポリアミド 酸)

- (g)ポリビニル系(例:ポリグリシジルメタクリレート、ポリビニルケイ 皮酸エステル)

の順にドライエッチング耐性が高いので、これに応じて第1レジスト膜にエッチ ング耐性の低い、例えば(g)のポリビニル系の有機材料を、第2レジスト膜に エッチング耐性の高い、例えば(a)のノボラック系樹脂を選定する。

(2)ドライエッチングによりエッチング中にエッチング耐性のある膜に改質す るレジスト膜を予め選定し、第2レジスト膜として堆積させておく場合、第1レ ジスト膜として、例えば(1)で示した(a)~(g)のいずれかの有機材料を 選定し、第2レジスト膜として、次のような無機材料を含有するレジスト膜を堆 積させる。

[0101]

(h) Si含有レジスト:

シロキサン、ポリシロキサン、ポリシラン、ポリシリーン、カルボシ ランを含むレジスト

(i) S i 以外の金属含有レジスト:

ゲルマニウム、カルコゲナイドガラス(例:Se-Ge薄膜)、ヘテ ロポリタングステン酸、金属ハロゲン物(例:塩化カドミウム、フッ 化アルミニウム、LiF、ALF<sub>3</sub>をドープしたLiF)

次に、第1レジスト膜のエッチング除去は、1)ドライエッチング及び2)ウ

3 5

出証特2001-3082580

ェットエッチングの両方が考えられる。すなわち、1)ドライエッチングにおいては、 $O_2$ ガス、フッ素系ガス、又は $O_2$ ガスとフッ素系ガスの混合ガスのいずれかのプラズマ処理ガスを用いて行われ、プラズマ処理ガスがフッ素系ガスであるときは、SF<sub>6</sub>、CF<sub>4</sub>、CHF<sub>3</sub>のいずれかを含むガスであり、プラズマ処理ガスがO<sub>2</sub>ガスとフッ素系ガスの混合ガスであるときは、SF<sub>6</sub>/O<sub>2</sub>、CF<sub>4</sub>/O<sub>2</sub>、CHF<sub>3</sub>/O<sub>2</sub>のいずれかのガスを含むプラズマ処理ガスを用いる。

[0102]

また、2)ウェットエッチングにおいては、すなわちテトラメチルアンモニウ ムハイドロオキサイド、コリン、有機アミン等の有機アルカリ溶液や、KOH、 NAOH、Ca(OH)<sub>2</sub>、CaCO<sub>3</sub>等のいずれかを含む等の無機アルカリ溶液 が選ばれる。これは、このウェットエッチングが、上層の第2レジスト膜にシリ ル化が可能なレジスト膜を用い、第2レジスト膜をシラザンを含むシリル化剤に 浸漬しシリル化させ、さらに酸素を含むガスでのドライエッチングによりシリコ ン酸化膜に改質してエッチング耐性を持つようにする場合に適用できることを意 味している。その他に、このウェットエッチングは、ドライエッチングに対する エッチング耐性のあるレジスト膜として既に挙げた(1)当初よりエッチング耐 性のあるレジスト膜を塗布形成する場合、(2)ドライエッチングによりエッチ ング中にエッチング耐性のある膜に改質するレジスト膜を予め選定し、第2レジ スト膜として堆積させておく場合に対しても適用できる。

[0103]

さらに、本発明は、上述した横電界型の液晶表示装置に限定されることなく、 縦電界型の液晶表示装置(例えば、TFTのソース電極の上のコンタクトホール)にも容易に適用可能な技術であることは自明のことである。

[0104]

また、本発明の第3、4、5の実施形態は、逆スタガード型のTFTパターン までの形成方法であるが、本発明のパターン形成方法はこれに限らず、前記TF Tパターンの形成方法のうち、画素電極の下部に色(カラーフィルタ)層、又は 平坦化膜と色(カラーフィルタ)層を形成したカラーフィルタ付きTFTパター ンの形成方法でも実施可能である。

[0105]

最後に、上述の本発明の第1~5の実施形態に示すパターン形成方法は、例え ばフラットディスプレイパネルの液晶表示装置(LCD)、エレクトロルミネッ センス表示装置(EL)、フィールドエミッションディスプレイ(FED)、蛍 光表示装置、プラズマディスプレイパネル(PDP)のアクティブ素子基板、ま たは、集積回路を備えた基板の製造工程において製造方法として用いられる。

[0106]

【発明の効果】

以上に説明したように、本発明のパターン形成方法及びそれを用いた液晶表示 装置の製造方法では、レジストマスクの膜厚の違いを利用して従来の2PR工程 1PR工程で済ませる際に、レジストマスクのうち薄い方のレジストマスクをエ ッチング除去するプロセスがあるが、この除去プロセスが開始されるときに、厚 い方のレジストマスクの上層をエッチングされにくい膜質に改質するので、厚い 方のレジストマスクはその平面形状をエッチング前の形状に維持することができ る。従って、厚い方のレジストマスクがエッチングされて残るレジストマスクを マスクとして得られるエッチングパターンの形状は、設計値に近い形状となり、 エッチング処理を受けた後に残るレジストマスクのパターンの形状を所望の形状 にしながら工程を簡略化することが可能となる。

【図面の簡単な説明】

【図1】

本発明の第1の実施形態を製造工程順に示す断面図である。

【図2】

図1に続く製造工程を示す断面図である。

【図3】

本発明の第2の実施形態を製造工程順に示す断面図である。

【図4】

図3に続く製造工程を示す模式断面図である。

【図5】

図4に続く製造工程を示す断面図である。

【図6】

本発明の第3の実施形態の平面図及び断面図である。

【図7】

本発明の第3の実施形態を製造工程順に示す断面図である。

【図8】

図7に続く製造工程を示す断面図である。

【図9】

図8に続く製造工程を示す断面図である。

【図10】

図9に続く製造工程を示す断面図である。

【図11】

図10に続く製造工程を示す断面図である。

【図12】

図11に続く製造工程を示す断面図である。

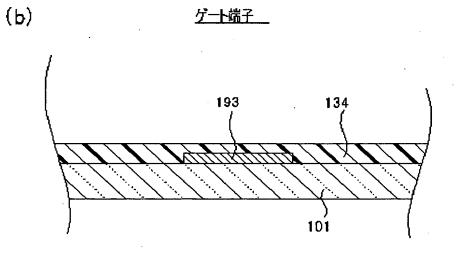

【図13】

図12に続く製造工程を示す断面図である。

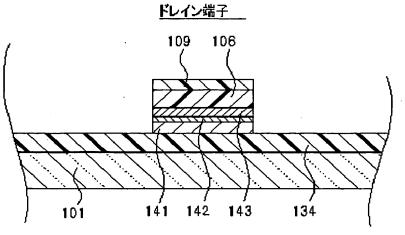

【図14】

図13に続く製造工程を示す断面図である。

【図15】

本発明の第4の実施形態の製造工程を示す断面図である。

【図16】

図15に続く製造工程を示す断面図である。

【図17】

図16に続く製造工程を示す断面図である。

【図18】

本発明の第5の実施形態の液晶表示装置を示す断面図である。

【図19】

図18に続く製造工程を示す断面図である。

【図20】

図19に続く製造工程を示す断面図である。

【図21】

図20に続く製造工程を示す断面図である。

【図22】

図21に続く製造工程を示す断面図である。

【図23】

第1の従来例の製造工程を示す断面図である。

【図24】

図23に続く製造工程を示す断面図である。

【図25】

第2の従来例の製造工程を示す模式断面図である。

【符号の説明】

1、21 絶縁基板

2 被エッチング膜

3、23、103、323、423 第1レジスト膜

4、24、104、324、424 第2レジスト膜

5、105 レジスト凹部

6、7、11、31、106、107、111、331、431 レジスト マスク

8、108 アイランド

9、29、109 シリル化膜

10、30、110、330、430 シリカ膜

12、112 凹部

26、326 薄レジストマスク

27、327 厚レジストマスク

33 下層配線

34 絶縁膜

35、135、155、335、355、435、455 コンタクトホー

ル

特2001-058138

- 36 上層金属膜

- 37 上層配線

- 67 残存レジストマスク

- 100 TFT基板

- 101、501、601 第1透明基板

- 133、533、633 ゲート電極

- 134、534、634 ゲート絶縁膜

- 137、437 ゲート端子透明電極

- 138 ドレイン配線

- 139 画素電極

- 140、340、440、640 パッシベーション膜

- 141、541、641 a-Si膜

- 142、542、642 n<sup>+</sup>型a-Si膜

- 143、543 金属膜

- 144、145、146、147 オーミック層

- 153 ゲート配線

- 157、457 ドレイン端子透明電極

- 158、658 ドレイン電極

- 159、659 ソース電極

- 173 共通電極

- 178、678 ドレイン端子電極

- 182、282 偏光板

- 193、693 ゲート端子電極

- 200 CF基板

- 201 第2透明基板

- 280 配向膜

- 281 液晶

- 283 光

- 284 ブラックマトリクス

- 285 色層

- 286 第2絶縁膜

- 287 導電膜

- 325、388、425、488 開口部

- 436 透明金属膜

- 526、527、626、627 感光膜パターン

- 660 a-Si 膜分離部

# 特2001-058138

出証特2001-3082580

(a)

(b)

# 出証特2001-3082580

【図4】

(a)

(b)

【図5】

(a)

(ь)

【図6】

(a)

【図7】

(c)

【図9】

出証特2001-3082580

【図10】

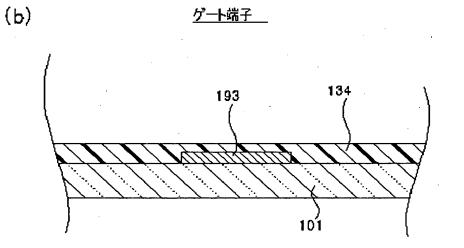

<u>ゲート端子</u>

(b)

【図11】

(b)

193 134 193 134 101

<u>ゲート端子</u>

## 出証特2001-3082580

【図12】

<u>ゲート端子</u>

(c)

<u>ドレイン端子</u>

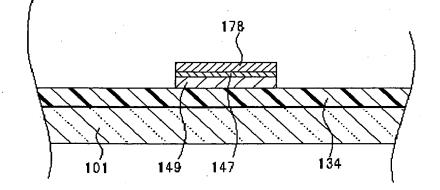

【図13】

(a) A

#### 出証特2001-3082580

.

(a) A

#### 特2001-058138

【図15】

(c)

【図16】

(c)

【図17】

<u>ドレイン端子</u>

## 特2001-058138

【図18】

١,

(c)

【図19】

(c)

ドレイン端子

【図20】

(c)

【図21】

(c)

【図22】

(c)

<u>ドレイン端子</u>

【図23】

【図24】

【図25】

(c)

【書類名】 要約書

【要約】

【課題】露光量の違いを利用して膜厚の異なる感光膜パターンを形成し、その膜 厚の差を利用してその下の被エッチング膜をエッチングして製造工程の短縮を図 る場合、感光膜パターンのうち薄い方の感光膜パターンがエッチング除去された ときに厚い方の感光膜パターンも同時にエッチングされ、その形状はエッチング 前の形状とは大幅に異なってしまうという問題がある。

【解決手段】レジスト凹部5の薄い方の感光膜パターンをエッチング除去すると きに、厚い方の感光膜パターンの上層9をエッチングされにくいシリカ膜10に 改質するので、厚い方の感光膜パターンはその平面形状をエッチング前の形状に 維持することができる。従って、薄い方の感光膜パターンがエッチングされて残 るシリカ膜10及びレジストマスク11をマスクとして得られるエッチングパタ ーンの形状8は、設計値に近い形状となる。

1

【選択図】 図2

## 特2001-058138

#### 認定・付加情報

| 特許出願の番号 | 特願 | 2 | 0 | 0  | 1 |    | 05 | 58 | 1 | 3 | 8 |    |   |  |

|---------|----|---|---|----|---|----|----|----|---|---|---|----|---|--|

| 受付番号    | 50 | 1 | 0 | 0  | 2 | 9  | 76 | 37 | 5 |   |   |    |   |  |

| 書類名     | 特許 | 顅 |   |    |   |    |    |    |   |   |   |    |   |  |

| 担当官     | 第二 | 担 | 当 | Ŀ, | 席 |    |    |    |   |   | 0 | 09 | 1 |  |

| 作成日     | 平成 | 1 | 3 | 年  |   | 3, | 月  | 5  | 日 |   |   |    |   |  |

|         |    |   |   |    |   |    |    |    |   |   |   |    |   |  |

<認定情報・付加情報>

۰,

(\_

【提出日】

平成13年 3月 2日

## 次頁無

## 特2001-058138

## 出願人履歴情報

識別番号

.

٢

# [0 0 0 1 8 1 2 8 4]

| 1. 変更年月日 | 1990年 8月10日     |

|----------|-----------------|

| [変更理由]   | 新規登録            |

| 住 所      | 鹿児島県出水市大野原町2080 |

| 氏 名      | 鹿児島日本電気株式会社     |